MC56F8323EVM Freescale Semiconductor, MC56F8323EVM Datasheet - Page 87

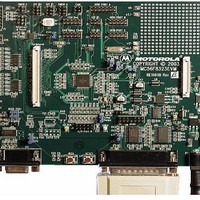

MC56F8323EVM

Manufacturer Part Number

MC56F8323EVM

Description

KIT EVALUATION FOR MC56F8323

Manufacturer

Freescale Semiconductor

Type

DSPr

Datasheets

1.CWH-UTP-ONCE-HE.pdf

(2 pages)

2.MC56F8323EVM.pdf

(72 pages)

3.MC56F8323EVME.pdf

(140 pages)

Specifications of MC56F8323EVM

Contents

Module and Misc Hardware

Processor To Be Evaluated

MC56F8322 and MC56F8323

Data Bus Width

16 bit

Interface Type

RS-232

For Use With/related Products

MC56F8322, MC56F8323

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

- Current page: 87 of 140

- Download datasheet (742Kb)

6.5.1.2

6.5.1.3

Writing 1 to this field will cause the part to reset.

6.5.1.4

6.5.1.5

6.5.2

Bits in this register are set upon any system reset and are initialized only by a Power-On Reset (POR). A

reset (other than POR) will only set bits in the register; bits are not cleared. Only software should clear this

register.

6.5.2.1

This bit field is reserved or not implemented. It is read as 0 and cannot be modified by writing.

6.5.2.2

When 1, this bit indicates that the previous reset occurred as a result of a software reset (write to SW RST

bit in the SIM CONTROL register). This bit will be cleared by any hardware reset or by software. Writing

a 0 to this bit position will set the bit, while writing a 1 to the bit will clear it.

Freescale Semiconductor

Preliminary

•

•

•

•

•

•

•

•

•

•

Base + $1

RESET

0 = OnCE clock to 56800E core enabled when core TAP is enabled

1 = OnCE clock to 56800E core is always enabled

00 = Stop mode will be entered when the 56800E core executes a STOP instruction

01 = The 56800E STOP instruction will not cause entry into Stop mode; STOP_DISABLE can be

reprogrammed in the future

10 = The 56800E STOP instruction will not cause entry into Stop mode; STOP_DISABLE can then only be

changed by resetting the device

11 = Same operation as 10

00 = Wait mode will be entered when the 56800E core executes a WAIT instruction

01 = The 56800E WAIT instruction will not cause entry into Wait mode; WAIT_DISABLE can be

reprogrammed in the future

10 = The 56800E WAIT instruction will not cause entry into Wait mode; WAIT_DISABLE can then only

be changed by resetting the device

11 = Same operation as 10

Read

Write

SIM Reset Status Register (SIM_RSTSTS)

OnCE Enable (ONCE EBL)—Bit 5

Software Reset (SW RST)—Bit 4

Stop Disable (STOP_DISABLE)—Bits 3–2

Wait Disable (WAIT_DISABLE)—Bits 1–0

Reserved—Bits 15–6

Software Reset (SWR)—Bit 5

15

0

0

Figure 6-4 SIM Reset Status Register (SIM_RSTSTS)

14

0

0

13

0

0

12

0

0

56F8323 Technical Data, Rev. 17

11

0

0

10

0

0

9

0

0

8

0

0

7

0

0

6

0

0

SWR

5

COPR

4

EXTR

3

POR

Register Descriptions

2

1

0

0

0

0

0

87

Related parts for MC56F8323EVM

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: