MC56F8323EVM Freescale Semiconductor, MC56F8323EVM Datasheet - Page 97

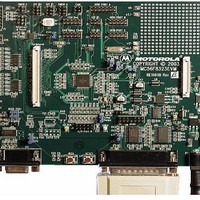

MC56F8323EVM

Manufacturer Part Number

MC56F8323EVM

Description

KIT EVALUATION FOR MC56F8323

Manufacturer

Freescale Semiconductor

Type

DSPr

Datasheets

1.CWH-UTP-ONCE-HE.pdf

(2 pages)

2.MC56F8323EVM.pdf

(72 pages)

3.MC56F8323EVME.pdf

(140 pages)

Specifications of MC56F8323EVM

Contents

Module and Misc Hardware

Processor To Be Evaluated

MC56F8322 and MC56F8323

Data Bus Width

16 bit

Interface Type

RS-232

For Use With/related Products

MC56F8322, MC56F8323

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

- Current page: 97 of 140

- Download datasheet (742Kb)

6.5.10.2

This field represents the lower 16 address bits of the “hard coded” I/O short address.

6.6 Clock Generation Overview

The SIM uses an internal master clock from the OCCS (CLKGEN) module to produce the peripheral and

system (core and memory) clocks. The maximum master clock frequency is 120MHz. Peripheral and

system clocks are generated at half the master clock frequency and therefore at a maximum 60MHz. The

SIM provides power modes (Stop, Wait) and clock enables (SIM_PCE register, CLK_DIS, ONCE_EBL)

to control which clocks are in operation. The OCCS, power modes, and clock enables provide a flexible

means to manage power consumption.

Power utilization can be minimized in several ways. In the OCCS, the relaxation oscillator, crystal

oscillator, and PLL may be shut down when not in use. When the PLL is in use, its prescaler and postscaler

can be used to limit PLL and master clock frequency. Power modes permit system and/or peripheral clocks

to be disabled when unused. Clock enables provide the means to disable individual clocks. Some

peripherals provide further controls to disable unused subfunctions. Refer to

Synthesis

The memory, peripheral and core clocks all operate at the same frequency (60MHz max).

6.7 Power-Down Modes

The 56F8323/56F8123 operate in one of three power-down modes, as shown in

All peripherals, except the COP/watchdog timer, run off the IPBus clock frequency, which is the same as

the main processor frequency in this architecture. The maximum frequency of operation is SYS_CLK =

60MHz.

Refer to the PCE register in

frequency, which can be controlled through the OCCS.

Freescale Semiconductor

Preliminary

Run

Wait

Stop

Mode

(OCCS), and the 56F8300 Peripheral User Manual for further details.

Input/Output Short Address Low (ISAL[21:6])—Bit 15–0

Active

Core and memory

clocks disabled

System clocks continue to be generated in

the SIM, but most are gated prior to

reaching memory, core and peripherals.

Table 6-2 Clock Operation in Power-Down Modes

Core Clocks

Part 6.5.9

56F8323 Technical Data, Rev. 17

Active

Active

Peripheral Clocks

and ADC power modes. Power is a function of the system

Device is fully functional

Peripherals are active and can produce

interrupts if they have not been masked off.

Interrupts will cause the core to come out of its

suspended state and resume normal operation.

Typically used for power-conscious applications.

The only possible recoveries from Stop mode

are:

1. CAN traffic (1st message will be lost)

2. Non-clocked interrupts (IRQA)

3. COP reset

4. External reset

5. Power-on reset

Description

Table 6-2

Part 3 On-Chip Clock

Clock Generation Overview

.

97

Related parts for MC56F8323EVM

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: