MC56F8323EVM Freescale Semiconductor, MC56F8323EVM Datasheet - Page 98

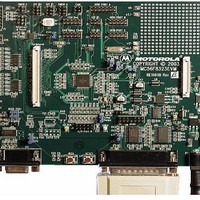

MC56F8323EVM

Manufacturer Part Number

MC56F8323EVM

Description

KIT EVALUATION FOR MC56F8323

Manufacturer

Freescale Semiconductor

Type

DSPr

Datasheets

1.CWH-UTP-ONCE-HE.pdf

(2 pages)

2.MC56F8323EVM.pdf

(72 pages)

3.MC56F8323EVME.pdf

(140 pages)

Specifications of MC56F8323EVM

Contents

Module and Misc Hardware

Processor To Be Evaluated

MC56F8322 and MC56F8323

Data Bus Width

16 bit

Interface Type

RS-232

For Use With/related Products

MC56F8322, MC56F8323

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

- Current page: 98 of 140

- Download datasheet (742Kb)

6.8 Stop and Wait Mode Disable Function

The 56800E core contains both STOP and WAIT instructions. Both put the CPU to sleep. For lowest

power consumption in Stop mode, the PLL can be shut down. This must be done explicitly before entering

Stop mode, since there is no automatic mechanism for this. When the PLL is shut down, the 56800E

system clock must be set equal to the prescaler output.

Some applications require the 56800E STOP and WAIT instructions be disabled. To disable those

instructions, write to the SIM control register (SIM_CONTROL) described in

can be on either a permanent or temporary basis. Permanently assigned applications last only until their

next reset.

6.9 Resets

The SIM supports four sources of reset. The two asynchronous sources are the external RESET pin and

the Power-On Reset (POR). The two synchronous sources are the software reset, which is generated within

the SIM itself, by writing to the SIM_CONTROL register, and the COP reset.

Reset begins with the assertion of any of the reset sources. Release of reset to various blocks is sequenced

to permit proper operation of the device. A POR reset is declared when reset is removed and any of the

three voltage detectors (1.8V POR, 2.2V core voltage, or 2.7V I/O voltage) indicate a low supply voltage

condition. POR will continue to be asserted until all voltage detectors indicate a stable supply is available

(note that as power is removed POR is not declared until the 1.8V core voltage threshold is reached.) A

POR reset is then extended for 64 clock cycles to permit stabilization of the clock source, followed by a

32 clock window in which SIM clocking is initiated. It is then followed by a 32 clock window in which

peripherals are released to implement Flash security, and, finally, followed by a 32 clock window in which

the core is initialized. After completion of the described reset sequence, application code will begin

execution.

Resets may be asserted asynchronously, but are always released internally on a rising edge of the system

clock.

98

Permanent

Disable

Reprogrammable

Disable

Clock

Select

Figure 6-16 Internal Stop Disable Circuit

Reset

56F8323 Technical Data, Rev. 17

D

D-FLOP

C R

D

D

D-FLOP

C

Q

Q

Note: Wait disable

circuit is similar

STOP_DIS

56800E

Part

6.5.1. This procedure

Freescale Semiconductor

Preliminary

Related parts for MC56F8323EVM

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: