EP9315-IBZ Cirrus Logic Inc, EP9315-IBZ Datasheet - Page 138

EP9315-IBZ

Manufacturer Part Number

EP9315-IBZ

Description

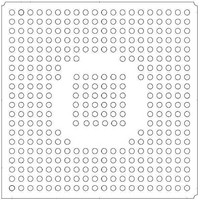

32-Bit Microcontroller IC

Manufacturer

Cirrus Logic Inc

Series

EP9r

Specifications of EP9315-IBZ

Controller Family/series

(ARM9)

Core Size

32 Bit

A/d Converter

12 Bits

Supply Voltage

3.3V

No. Of I/o Pins

65

Package / Case

352-PBGA

Clock Frequency

200MHz

Core Processor

ARM9

Speed

200MHz

Connectivity

EBI/EMI, EIDE, Ethernet, I²C, IrDA, Keypad/Touchscreen, PCMCIA, SPI, UART/USART, USB

Peripherals

AC'97, DMA, I²:S, LCD, LED, MaverickKey, POR, PWM, WDT

Number Of I /o

16

Program Memory Type

ROMless

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 3.6 V

Data Converters

A/D 8x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Processor Series

EP93xx

Core

ARM920T

Data Bus Width

32 bit

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

EDB9315A-Z

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

598-1144 - KIT DEVELOPMENT EP9315 ARM9

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Details

Other names

598-1263

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

13

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

347

- Current page: 138 of 824

- Download datasheet (13Mb)

5

5-12

5.1.6.2.3

5.1.6.2.4

5.1.6.2.5

System Controller

EP93xx User’s Guide

5.1.7 Interrupt Generation

set. One example of this is when a power-on-reset is applied and this register bit is cleared.

This means that this bit will not be set on boot-up and will have to be set to maintain the

memory image for when the device re-enters Standby mode.

A transition from Run mode to Halt mode is caused by reading the Halt register location

0x8093_0008 with the SHena bit set to 1. This has the effect of gating the CPU clock (FCLK)

bus interface, with the APB/AHB system clock, and Memory/DMA system remaining enabled.

There are normally several conditions in which the device can move from Standby mode to

Run mode.

These conditions are:

The EP93xx comes out of Standby if an interrupt occurs or when an exit from a ClkSet1 write

occurs. If a write is performed to the ClkSet1 register, the EP93xx then enters Standby mode

and then automatically comes out of Standby mode and back into the Run state.

The transition from the Halt state to the Run state is caused by:

The Syscon block generates two interrupts: TICK interrupt and Watchdog Expired interrupt.

The block generates the TICK interrupt based upon the 64 Hz clock, which is derived from

the 32.768 KHz oscillator. The interrupt becomes active on every rising edge of the internal

64 Hz clock. It can be cleared by writing to the TEOI location.

Watchdog Expired interrupt becomes active on a rising edge of the 64 Hz TICK clock, if the

TICK interrupt is still active. In other words, if a TICK interrupt has not been served for a

complete TICK period, a watchdog expired interrupt is generated. It can be cleared by writing

to the TEOI location as well.

• A falling edge on IRQ interrupt

• A falling edge on FIQ interrupt

• An exit from a

• PRSTn

• RSTOn

• A falling edge on IRQ interrupt

• A falling edge on FIQ interrupt

• RSTOn

RUN HALT mode

STANDBY RUN mode

HALT RUN mode

"ClkSet1"

write

Copyright 2007 Cirrus Logic

DS785UM1

Related parts for EP9315-IBZ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC ARM9 SOC ENH UNIV 352PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Eval Bd Uni. ARM9 SOC Processor

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

High-efficiency PFC + Fluorescent Lamp Driver Reference Design

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Ref Bd For Speakerbar MSA & DSP Products

Manufacturer:

Cirrus Logic Inc