EP9315-IBZ Cirrus Logic Inc, EP9315-IBZ Datasheet - Page 191

EP9315-IBZ

Manufacturer Part Number

EP9315-IBZ

Description

32-Bit Microcontroller IC

Manufacturer

Cirrus Logic Inc

Series

EP9r

Specifications of EP9315-IBZ

Controller Family/series

(ARM9)

Core Size

32 Bit

A/d Converter

12 Bits

Supply Voltage

3.3V

No. Of I/o Pins

65

Package / Case

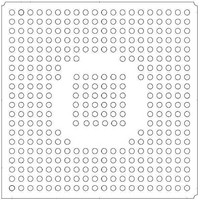

352-PBGA

Clock Frequency

200MHz

Core Processor

ARM9

Speed

200MHz

Connectivity

EBI/EMI, EIDE, Ethernet, I²C, IrDA, Keypad/Touchscreen, PCMCIA, SPI, UART/USART, USB

Peripherals

AC'97, DMA, I²:S, LCD, LED, MaverickKey, POR, PWM, WDT

Number Of I /o

16

Program Memory Type

ROMless

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 3.6 V

Data Converters

A/D 8x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Processor Series

EP93xx

Core

ARM920T

Data Bus Width

32 bit

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

EDB9315A-Z

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

598-1144 - KIT DEVELOPMENT EP9315 ARM9

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Details

Other names

598-1263

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

13

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

347

- Current page: 191 of 824

- Download datasheet (13Mb)

DS785UM1

7.4.2 Video FIFO

register,

corner of the lower half of the display begins at the word address stored in the

“VidScrnHPage”

load address counters at the beginning of the video frame.

The VILOSATI continues to service the video FIFO until it has transferred an entire screen

image from memory. The size of the screen image is controlled by the values stored in the

“ScrnLines”

displayed (active) lines for the video frame. The

words for each displayed (active) video line. A separate register,

defines the word offset in memory between the beginning of each line and the next line.

Setting the VLineStep value larger than the LineLength value provides the capability for

image panning as shown in

The video FIFO is used to buffer data transferred from the image memory to the Video output

circuitry without stalling the video data stream. The FIFO consists of a dual port RAM with

input and output index counters and control circuitry to operate it as a FIFO memory. The

input data bus width to the FIFO is 32 bits. During half page mode, when the display requires

scan out of the bottom and top half of the screen at the same time (dual scan), top half (or

bottom half) data is stored in every other FIFO location.

When the screen is single scan (scanned out as a single progressive image), FIFO data is

stored sequentially. The FIFO output data bus is 64 bits wide and can output even and odd

“VidScrnPage” on page

and

register. The

“LineLength”

(Dual Scan mode only)

Figure

Figure 7-2. Video Buffer Diagram

VIDSCRNPAGE

“VidScrnPage”

Copyright 2007 Cirrus Logic

start address

start address

registers. The

VIDSCRHPG

7-46. For a dual scan display, information from the upper left

7-2.

Raster Engine With Analog/LCD Integrated Timing and Interface

LINELENGTH + 1

Displayed Portion

Frame Buffer

VLINESTEP

“ScrnLines”

and

“LineLength”

“VidScrnHPage”

register defines the total number of

register defines the number of

“VLineStep” on page

registers are used to pre-

EP93xx User’s Guide

7-48,

7-9

7

Related parts for EP9315-IBZ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC ARM9 SOC ENH UNIV 352PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Eval Bd Uni. ARM9 SOC Processor

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

High-efficiency PFC + Fluorescent Lamp Driver Reference Design

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Ref Bd For Speakerbar MSA & DSP Products

Manufacturer:

Cirrus Logic Inc