EP9315-IBZ Cirrus Logic Inc, EP9315-IBZ Datasheet - Page 312

EP9315-IBZ

Manufacturer Part Number

EP9315-IBZ

Description

32-Bit Microcontroller IC

Manufacturer

Cirrus Logic Inc

Series

EP9r

Specifications of EP9315-IBZ

Controller Family/series

(ARM9)

Core Size

32 Bit

A/d Converter

12 Bits

Supply Voltage

3.3V

No. Of I/o Pins

65

Package / Case

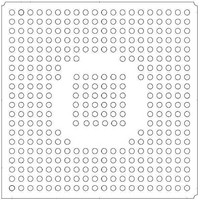

352-PBGA

Clock Frequency

200MHz

Core Processor

ARM9

Speed

200MHz

Connectivity

EBI/EMI, EIDE, Ethernet, I²C, IrDA, Keypad/Touchscreen, PCMCIA, SPI, UART/USART, USB

Peripherals

AC'97, DMA, I²:S, LCD, LED, MaverickKey, POR, PWM, WDT

Number Of I /o

16

Program Memory Type

ROMless

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 3.6 V

Data Converters

A/D 8x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Processor Series

EP93xx

Core

ARM920T

Data Bus Width

32 bit

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

EDB9315A-Z

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

598-1144 - KIT DEVELOPMENT EP9315 ARM9

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Details

Other names

598-1263

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

13

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

347

- Current page: 312 of 824

- Download datasheet (13Mb)

9

9-10

1/10/100 Mbps Ethernet LAN Controller

EP93xx User’s Guide

9.1.4.7 Flow Control

9.1.4.8 Receive Flow Control

9.1.4.9 Transmit Flow Control

The relationship of RXCtl.MA and RXCtl.IAHA is shown below.

The MAC provides special support for flow control by the transmission and reception of

pause frames. A pause frame is a specific format of a MAC control frame that defines an

amount of time for a transmitter to stop sending frames. Sending pause frames thereby

reduces the amount of data sent by the remote station.

The MAC can detect receive pause frames and automatically stop the transmitter for the

appropriate period of time. To be interpreted as a pause frame the following conditions must

be met:

If accepted as a pause frame, the pause time field is transferred to the Flow Control Timer

register. The pause frame may be optionally passed on to the Host or discarded by the MAC.

Once the Flow Control Timer is set to a non-zero value, no new transmit frames are started,

until the count reaches zero. The counter is decremented once every slot time while no frame

is being transmitted.

When receive congestion is detected, the driver may want to transmit a pause frame to the

remote station to create time for the local receiver to free resources. As there may be many

frames queued in the transmitter, and there is a chance that the local transmitter is itself

being paused, an alternative method is provided to allow a pause frame to be transmitted.

Setting the Send Pause bit in the Transmit Control register causes a pause frame to be

transmitted at the earliest opportunity. This occurs either immediately, or following the

completion of the current transmit frame. If the local transmitter is paused, the pause frame

will still be sent, and the pause timer will still be decremented during the frame transmission.

• Destination address accepted by one of the first two individual address filters, with the

• The Type field must match that programmed in the Flow Control Format register.

• The next two bytes of the frame (MAC Control Opcode) must equal 0x0001.

• The frame must be of legal length with a good CRC.

appropriate RXCtl.RxFCE bit set.

RXCtl.MA

0

1

0

1

RXCtl.IAHA[0]

Table 9-2. RXCtl.MA and RXCtl.IAHA[0] Relationships

0

0

1

1

Copyright 2007 Cirrus Logic

Hash filter not used in acceptance criteria.

All multicast frames (first bit of DA = 1) passing the hash are

accepted.

All individual address frames (first bit of DA = 0) passing the hash

are accepted.

All frames that pass the hash are accepted.

Hash Filter Acceptance Results

DS785UM1

Related parts for EP9315-IBZ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC ARM9 SOC ENH UNIV 352PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Eval Bd Uni. ARM9 SOC Processor

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

High-efficiency PFC + Fluorescent Lamp Driver Reference Design

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Ref Bd For Speakerbar MSA & DSP Products

Manufacturer:

Cirrus Logic Inc