EP9315-IBZ Cirrus Logic Inc, EP9315-IBZ Datasheet - Page 417

EP9315-IBZ

Manufacturer Part Number

EP9315-IBZ

Description

32-Bit Microcontroller IC

Manufacturer

Cirrus Logic Inc

Series

EP9r

Specifications of EP9315-IBZ

Controller Family/series

(ARM9)

Core Size

32 Bit

A/d Converter

12 Bits

Supply Voltage

3.3V

No. Of I/o Pins

65

Package / Case

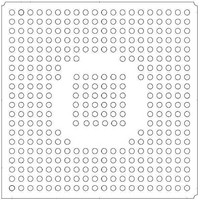

352-PBGA

Clock Frequency

200MHz

Core Processor

ARM9

Speed

200MHz

Connectivity

EBI/EMI, EIDE, Ethernet, I²C, IrDA, Keypad/Touchscreen, PCMCIA, SPI, UART/USART, USB

Peripherals

AC'97, DMA, I²:S, LCD, LED, MaverickKey, POR, PWM, WDT

Number Of I /o

16

Program Memory Type

ROMless

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 3.6 V

Data Converters

A/D 8x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Processor Series

EP93xx

Core

ARM920T

Data Bus Width

32 bit

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

EDB9315A-Z

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

598-1144 - KIT DEVELOPMENT EP9315 ARM9

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Details

Other names

598-1263

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

13

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

347

- Current page: 417 of 824

- Download datasheet (13Mb)

PPALLOC

DS785UM1

31

15

Address:

Definition:

Bit Descriptions:

Note:

30

14

allocation for both a transmit channel and a receive channel.

Two channels cannot be programmed to serve the same port since, in the case of an

erroneous software write operation, the lower channel number is given priority. For

example, if software writes the value 0x01 to Channel 0 Tx PPALLOC[3:0], and also writes

this same value to Channel 2 Tx PPALLOC[3:0], then the Channel 0 Tx will be configured

for Port 0 and Channel 2 will not function correctly.

The PPALLOC register must be written to before a channel is enabled. If this is not done,

then the default allocation of the ports will be used.

PPALLOC:Table

29

13

28

12

ABORT:

ICE:

Channel Base Address + 0x0008 - Read/Write

This is the Peripheral Port Allocation register used to configure the internal

M2P channel programmability. It is possible to program a channels use on one

of a number of different peripherals.

There can be 20 external peripherals - 10 Tx and 10 Rx - connected to the 20

“ports” of the DMA. The 10 internal M2P DMA channels can serve 10 of these

ports at one time.

RSVD:

27

11

10-5,

26

10

Table

RSVD

Copyright 2007 Cirrus Logic

25

9

10-6, and

This bit determines how the DMA Channel State machine

behaves while in the NEXT state and in receipt of a

peripheral error, indicated on RxEnd/TxEnd. This bit is

ignored when ICE is set.

0 - NEXT -> ON state, effectively ignoring the error.

1 - NEXT -> STALL state, effectively disabling the channel.

No STALLInt interrupt is set for this condition.

Ignore Channel Error bit. Setting this bit results in

suppression of the generation of the ChErrorInt interrupt

and does not result in buffer termination. This bit may be

set for data streams whereby the end user is tolerant to

occasional bit errors.

Reserved. Unknown During Read.

24

8

RSVD

Table 10-7

23

7

22

6

give the PPALLOC decode for the port

21

5

20

4

19

3

EP93xx User’s Guide

18

2

PPALLOC

DMA Controller

17

1

10-23

16

0

10

Related parts for EP9315-IBZ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC ARM9 SOC ENH UNIV 352PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Eval Bd Uni. ARM9 SOC Processor

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

High-efficiency PFC + Fluorescent Lamp Driver Reference Design

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Ref Bd For Speakerbar MSA & DSP Products

Manufacturer:

Cirrus Logic Inc