EP9315-IBZ Cirrus Logic Inc, EP9315-IBZ Datasheet - Page 505

EP9315-IBZ

Manufacturer Part Number

EP9315-IBZ

Description

32-Bit Microcontroller IC

Manufacturer

Cirrus Logic Inc

Series

EP9r

Specifications of EP9315-IBZ

Controller Family/series

(ARM9)

Core Size

32 Bit

A/d Converter

12 Bits

Supply Voltage

3.3V

No. Of I/o Pins

65

Package / Case

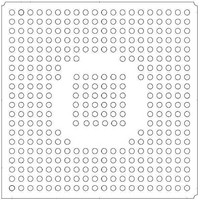

352-PBGA

Clock Frequency

200MHz

Core Processor

ARM9

Speed

200MHz

Connectivity

EBI/EMI, EIDE, Ethernet, I²C, IrDA, Keypad/Touchscreen, PCMCIA, SPI, UART/USART, USB

Peripherals

AC'97, DMA, I²:S, LCD, LED, MaverickKey, POR, PWM, WDT

Number Of I /o

16

Program Memory Type

ROMless

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 3.6 V

Data Converters

A/D 8x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Processor Series

EP93xx

Core

ARM920T

Data Bus Width

32 bit

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

EDB9315A-Z

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

598-1144 - KIT DEVELOPMENT EP9315 ARM9

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Details

Other names

598-1263

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

13

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

347

- Current page: 505 of 824

- Download datasheet (13Mb)

DS785UM1

13.8.1 Chip Select SDCSN[3:0] Decoding

13.8 External Synchronous Memory System

to the SyncFLASH register and the associated value on the data pins specifies which

SyncFLASH register is written. Actually, the value on the data pins specifies a command to

the SyncFLASH device such as Write Configuration Register, Lock Block, Block Erase; and

the associated value on the address pins specifies either a value that is written to a register

or a address location inside the SyncFLASH device.

Synchronous FLASH devices:

The synchronous memory system is decoded from the ARM Core’s physical memory map

into four independent address domains, each having an address range of 256 Mbytes (64

Mwords). All of the memory devices that are attached to a given domain must be of the same

type, but the other domains may use different memory device types and associated timing

characteristics.

Since all memory devices, synchronous or static, share a common external memory bus, the

total number of devices is limited by the maximum allowable bus capacitance.

Each of the four address domains within synchronous memory space have an associated

chip select signal that is output on one of the SDCSn[3:0] pins as shown in

signals are decoded from address bits A31:A28.

The latched value of ASDO determines how SDCSn3 is mapped into synchronous memory

space. If the latched value of ASDO=1 then SDCSn3 is mapped to 0x0000_0000 otherwise it

is mapped to 0xF000_0000.

• Use the same combination of the CS, RAS, CAS, and WE signals which would normally

• Cannot be written in bursts, but only one word at a time. Hence the requirement to write

• Require 100 μs of initialization time after a low-to-high transition occurs on its write

• Can be set up by either programming the Synchronous FLASH Configuration register

place an SDRAM device into Auto-Refresh mode

WBM = ‘1’ to the appropriate SDRAMDevCfg register. When WBM = ‘1’, no Auto

Refresh cycle will occur in the associated synchronous memory domain because the

synchronous memory controller will assume that a Synchronous FLASH device is

attached.

protect input pin

before releasing the processor from reset or by using the contents of it’s

NonVolatileMODE register (which must have been previously programmed).

Boot Option

(ASDO)

1

A31

0

Table 13-9. Chip Select Decoding

Copyright 2007 Cirrus Logic

A30

0

A29

0

SDRAM, SyncROM, and SyncFLASH Controller

A28

0

Chip select

nSDCS3

EP93xx User’s Guide

Table

13-9. These

13-9

13

Related parts for EP9315-IBZ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC ARM9 SOC ENH UNIV 352PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Eval Bd Uni. ARM9 SOC Processor

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

High-efficiency PFC + Fluorescent Lamp Driver Reference Design

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Ref Bd For Speakerbar MSA & DSP Products

Manufacturer:

Cirrus Logic Inc