EP9315-IBZ Cirrus Logic Inc, EP9315-IBZ Datasheet - Page 47

EP9315-IBZ

Manufacturer Part Number

EP9315-IBZ

Description

32-Bit Microcontroller IC

Manufacturer

Cirrus Logic Inc

Series

EP9r

Specifications of EP9315-IBZ

Controller Family/series

(ARM9)

Core Size

32 Bit

A/d Converter

12 Bits

Supply Voltage

3.3V

No. Of I/o Pins

65

Package / Case

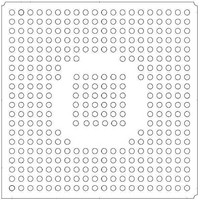

352-PBGA

Clock Frequency

200MHz

Core Processor

ARM9

Speed

200MHz

Connectivity

EBI/EMI, EIDE, Ethernet, I²C, IrDA, Keypad/Touchscreen, PCMCIA, SPI, UART/USART, USB

Peripherals

AC'97, DMA, I²:S, LCD, LED, MaverickKey, POR, PWM, WDT

Number Of I /o

16

Program Memory Type

ROMless

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 3.6 V

Data Converters

A/D 8x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Processor Series

EP93xx

Core

ARM920T

Data Bus Width

32 bit

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

EDB9315A-Z

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

598-1144 - KIT DEVELOPMENT EP9315 ARM9

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Details

Other names

598-1263

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

13

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

347

- Current page: 47 of 824

- Download datasheet (13Mb)

DS785UM1

2.2.7 Memory and Bus Access Errors

2.2.8 Bus Arbitration

A write data bus is used to move data from the master to a slave, while a read data bus is

used to move data from a slave to the master. Every transfer consists of:

In normal operation a master is allowed to complete all the transfers in a particular burst

before the arbiter grants another master access to the bus. However, in order to avoid

excessive arbitration latencies, it is possible for the arbiter to break up a burst, and, in such

cases, the master must re-arbitrate for the bus in order to complete the remaining transfers in

the burst.

There are several possible sources of access errors:

The arbitration mechanism is used to ensure that only one master has access to the bus that

it controls at any one time. The Arbiter performs this function by observing a number of

different requests to use the bus, and then deciding which is currently the highest priority

master requesting the bus.

The arbitration scheme can be broken down into three main areas:

• An address and control cycle

• One or more cycles for the data.

• Reads to reserved or undefined register memory addresses will return indeterminate

• Access to non-existent registers or memory may result in a bus error

• Any access to the APB control register space will complete normally, as these devices

• Access to non-existent AHB or APB registers may result in a bus error, depending on the

• External memory access is controlled by the Static Memory Controller (SMC) or the

• The main AHB system bus Arbiter

• The SDRAM slave interface Arbiter

• The EBI bus Arbiter

data. Writes to reserved or undefined memory addresses are generally ignored, but this

behavior is not guaranteed. Many register addresses are not fully decoded, so aliasing

may occur. Addresses and memory ranges listed as Reserved should not be accessed;

access behavior to these regions is not defined

have no means of signaling an error

device and nature of the error. Device specific access rules are defined in the device

descriptions

Synchronous Dynamic RAM (SDRAM) controller. In general, access to non-existent

external memory will complete normally, with reads returning random false data.

Copyright 2007 Cirrus Logic

ARM920T Core and Advanced High-Speed Bus (AHB)

EP93xx User’s Guide

2-9

2

Related parts for EP9315-IBZ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC ARM9 SOC ENH UNIV 352PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Eval Bd Uni. ARM9 SOC Processor

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

High-efficiency PFC + Fluorescent Lamp Driver Reference Design

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Ref Bd For Speakerbar MSA & DSP Products

Manufacturer:

Cirrus Logic Inc