P87C591VFA/00,512 NXP Semiconductors, P87C591VFA/00,512 Datasheet - Page 113

P87C591VFA/00,512

Manufacturer Part Number

P87C591VFA/00,512

Description

IC 80C51 MCU 16K OTP 44-PLCC

Manufacturer

NXP Semiconductors

Series

87Cr

Datasheet

1.P87C591VFA00512.pdf

(160 pages)

Specifications of P87C591VFA/00,512

Core Processor

8051

Core Size

8-Bit

Speed

12MHz

Connectivity

CAN, EBI/EMI, I²C, UART/USART

Peripherals

POR, PWM, WDT

Number Of I /o

32

Program Memory Size

16KB (16K x 8)

Program Memory Type

OTP

Ram Size

512 x 8

Voltage - Supply (vcc/vdd)

4.75 V ~ 5.25 V

Data Converters

A/D 6x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

44-PLCC

Processor Series

P87C5x

Core

80C51

Data Bus Width

8 bit

Data Ram Size

512 B

Interface Type

CAN, I2C, UART

Maximum Clock Frequency

12 MHz

Number Of Programmable I/os

32

Number Of Timers

3

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

PK51, CA51, A51, ULINK2

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 6 Channel

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Other names

568-1256-5

935268182512

P87C591VFAA

935268182512

P87C591VFAA

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

P87C591VFA/00,512

Manufacturer:

TI

Quantity:

8

Company:

Part Number:

P87C591VFA/00,512

Manufacturer:

NXP Semiconductors

Quantity:

10 000

Philips Semiconductors

16 TIMER 2

16.1

Timer T2 is a 16-bit timer consisting of two registers TMH2

(HIGH byte) and TML2 (LOW byte). The 16-bit

timer/counter can be switched off or clocked via a

prescaler from one of two sources: f

signal. When Timer T2 is configured as a counter, the

prescaler is clocked by an external signal on T2 (P3.O). A

rising edge on T2 increments the prescaler, and the

maximum repetition rate is one count per machine cycle

(1 MHz with a 6 MHz oscillator).

The maximum repetition rate for Timer T2 is twice the

maximum repetition rate for Timer 0 and Timer 1. T2 (P3.0)

is sampled at S2P1 and again at S5P1 (i.e., twice per

machine cycle). A rising edge is detected when T2 is LOW

during one sample and HIGH during the next sample. To

ensure that a rising edge is detected, the input signal must

be LOW for at least

cycle. If a rising edge is detected before the end of S2P1,

the timer will be incremented during the following cycle;

otherwise it will be incremented one cycle later. The

prescaler has a programmable division factor of 1, 2, 4, or

8 and is cleared if its division factor or input source is

changed, or if the timer/counter is reset.

Timer T2 may be read “on the fly” but possesses no extra

read latches, and software precautions may have to be

taken to avoid misinterpretation in the event of an overflow

from least to most significant byte while Timer T2 is being

read. Timer T2 is not loadable and is reset by the RST

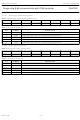

Table 66 Timer T2 Interrupt Enable Register IEN1 (address E8H)

Table 67 Description of interrupt Enable Register IEN1 bits

2000 Jul 26

Single-chip 8-bit microcontroller with CAN controller

ET2

BIT

7

7

6

5

4

3

2

1

0

Features of Timer 2

ECAN

SYMBOL

1

2

ECAN

ECM1

ECM0

ECT3

ECT2

ECT1

ECT0

6

ET2

cycle and then HIGH for at least

ECM1

Enable Timer T2 overflow interrupt(s).

Enable CAN interrupt.

Enable T2 Comparator 1 interrupt.

Enable T2 Comparator 0 interrupt.

Enable T2 Capture register 3 interrupt.

Enable T2 Capture register 2 interrupt.

Enable T2 Capture register 1 interrupt.

Enable T2 Capture register 0 interrupt.

CLK

5

/6 or an external

ECM0

4

1

2

113

signal or by a rising edge on the input signal RT2, if

enabled. RT2 is enabled by setting bit T2ER (TM2CON.5).

When the least significant byte of the timer overflows or

when a 16-bit overflow occurs, an interrupt request may be

generated. Either or both of these overflows can be

programmed to request an interrupt. In both cases, the

interrupt vector will be the same. When the lower byte

(TML2) overflows, flag T2B0 (TM2CON) is set and flag

T20V (TM2lR) is set when TMH2 overflows. These flags

are set one cycle after an overflow occurs. Note that when

T20V is set, T2B0 will also be set. To enable the byte

overflow interrupt, bits ET2 (lEN1.7, enable overflow

interrupt, see Table 67) and T2lS0 (TM2CON.6, byte

overflow interrupt select) must be set. Bit TWBO

(TM2CON.4) is the Timer T2 byte overflow flag. To enable

the 16-bit overflow interrupt, bits ET2 (lE1.7, enable

overflow interrupt) and T2lS1 (TM2CON.7, 16-bit overflow

interrupt select) must be set. Bit T2OV (TM2lR.7) is the

Timer T2 16-bit overflow flag. All interrupt flags must be

reset by software. To enable both byte and 16-bit overflow,

T2lS0 and T2lS1 must be set and two interrupt service

routines are required. A test on the overflow flags indicates

which routine must be executed. For each routine, only the

corresponding overflow flag must be cleared. Timer T2

may be reset by a rising edge on RT2 (P3.1) if the Timer

T2 external reset enable bit (T2ER) in TM2CON is set.

This reset also clears the prescaler. In the Idle mode, the

timer/counter and prescaler are reset and halted. Timer T2

is controlled by the TM2CON special function register (see

Section 16.1.1).

ECT3

3

FUNCTION

ECT2

2

ECT1

Preliminary Specification

1

P8xC591

ECT0

0