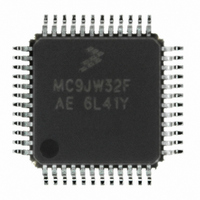

MCHC908JW32FAE Freescale Semiconductor, MCHC908JW32FAE Datasheet - Page 157

MCHC908JW32FAE

Manufacturer Part Number

MCHC908JW32FAE

Description

IC MCU 32K FLASH 8MHZ 48-LQFP

Manufacturer

Freescale Semiconductor

Series

HC08r

Datasheet

1.RD3152MMA7260Q.pdf

(232 pages)

Specifications of MCHC908JW32FAE

Core Processor

HC08

Core Size

8-Bit

Speed

8MHz

Connectivity

SPI, USB

Peripherals

LED, LVD, POR, PWM

Number Of I /o

29

Program Memory Size

32KB (32K x 8)

Program Memory Type

FLASH

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

3.5 V ~ 5.5 V

Oscillator Type

Internal

Operating Temperature

0°C ~ 70°C

Package / Case

48-LQFP

Controller Family/series

HC08

No. Of I/o's

48

Ram Memory Size

1KB

Cpu Speed

8MHz

No. Of Timers

1

Embedded Interface Type

SPI

Rohs Compliant

Yes

Processor Series

HC08JW

Core

HC08

Data Bus Width

8 bit

Data Ram Size

1 KB

Interface Type

SPI, USB

Number Of Programmable I/os

29

Number Of Timers

2

Maximum Operating Temperature

+ 70 C

Mounting Style

SMD/SMT

Development Tools By Supplier

FSICEBASE, DEMO908GZ60E, M68EML08GZE, KITUSBSPIDGLEVME, KITUSBSPIEVME, KIT33810EKEVME

Minimum Operating Temperature

0 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Data Converters

-

Lead Free Status / Rohs Status

Details

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MCHC908JW32FAE

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Part Number:

MCHC908JW32FAE

Manufacturer:

FREESCALE

Quantity:

20 000

SUSPND — SUSPEND Detection Flag

11.5.3 USB Status Interrupt Mask Register (USIMR)

EP0_STALL — Forced EP0 STALL Handshake Enable

SETUPIE — SETUP Request Interrupt Mask

SOFIE — Start-of-frame Interrupt Mask

CONFIG_CHGIE — Configuration Change Interrupt Mask

Freescale Semiconductor

This read/write bit is set when the module detects a suspend state on the USB bus or the bus is idle

for 3ms. The module will enter suspend mode when this bit is set. In order to reduce the power

consumption, user is recommended to stop the USB module clock by clearing the USBCLKEN bit in

USBCR register before putting the MCU in STOP mode. Writing zero to clear the bit. Writing one to

the bit has no effect. Reset clears this bit.

This write only bit is used to provide protocol STALL to the control endpoint. Writing one to the bit

causes endpoint 0 to return STALL in response to any IN or OUT token issue by the USB host until

the next SETUP transaction. The bit can only be erased by module hardware, writing zero to the bit

has no effect. Reset also clears this bit.

This read/write bit enables a CPU interrupt request when GET_DESCRIPTOR, SYNC_FRAME or

class/vendor specific request is received or SETUP flag of USB status register (USBSR) is set. Reset

clears this bit.

This read/write bit enables a CPU interrupt request when a start-of-frame signal is detected on the

USB bus or SOF flag of USB status register (USBSR) is set. Reset clears this bit.

This read/write bit enables a CPU interrupt request when a configuration change from zero to one is

detected or CONFIG_CHG flag of USB status register (USBSR) is set. Reset clears this bit.

1 = SUSPEND state is detected

0 = No suspend state is detected

1 = Send STALL handshake

0 = Do not response STALL handshaking

1 = CPU interrupt is enabled when SETUP flag in USBSR is set

0 = CPU interrupt is disabled when SETUP flag in USBSR is set

1 = SOF interrupt is enabled

0 = SOF interrupt is disabled

1 = CPU interrupt is enabled when CONFIG_CHG flag in USBSR is set

0 = CPU interrupt is disabled when CONFIG_CHG flag in USBSR is set

Address:

Reset:

Read:

Write:

$0053

Bit 7

R

R

0

Figure 11-5. USB Status Interrupt Mask Register

= Reserved

EP0_STALL

6

0

0

MC68HC908JW32 Data Sheet, Rev. 6

SETUPIE

5

0

SOFIE

4

0

CONFIG_

CHGIE

3

0

USBRE-

SETIE

2

0

RESUME-

FIE

1

0

USB Module Registers

SUSP-

NDIE

Bit 0

0

157