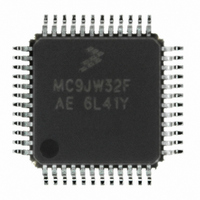

MCHC908JW32FAE Freescale Semiconductor, MCHC908JW32FAE Datasheet - Page 81

MCHC908JW32FAE

Manufacturer Part Number

MCHC908JW32FAE

Description

IC MCU 32K FLASH 8MHZ 48-LQFP

Manufacturer

Freescale Semiconductor

Series

HC08r

Datasheet

1.RD3152MMA7260Q.pdf

(232 pages)

Specifications of MCHC908JW32FAE

Core Processor

HC08

Core Size

8-Bit

Speed

8MHz

Connectivity

SPI, USB

Peripherals

LED, LVD, POR, PWM

Number Of I /o

29

Program Memory Size

32KB (32K x 8)

Program Memory Type

FLASH

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

3.5 V ~ 5.5 V

Oscillator Type

Internal

Operating Temperature

0°C ~ 70°C

Package / Case

48-LQFP

Controller Family/series

HC08

No. Of I/o's

48

Ram Memory Size

1KB

Cpu Speed

8MHz

No. Of Timers

1

Embedded Interface Type

SPI

Rohs Compliant

Yes

Processor Series

HC08JW

Core

HC08

Data Bus Width

8 bit

Data Ram Size

1 KB

Interface Type

SPI, USB

Number Of Programmable I/os

29

Number Of Timers

2

Maximum Operating Temperature

+ 70 C

Mounting Style

SMD/SMT

Development Tools By Supplier

FSICEBASE, DEMO908GZ60E, M68EML08GZE, KITUSBSPIDGLEVME, KITUSBSPIEVME, KIT33810EKEVME

Minimum Operating Temperature

0 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Data Converters

-

Lead Free Status / Rohs Status

Details

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MCHC908JW32FAE

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Part Number:

MCHC908JW32FAE

Manufacturer:

FREESCALE

Quantity:

20 000

If the stop enable bit, STOP, in the mask option register is logic 0, the SIM treats the STOP instruction as

an illegal opcode and causes an illegal opcode reset. The SIM actively pulls down the RST pin for all

internal reset sources.

6.3.2.4 Illegal Address Reset

An opcode fetch from an unmapped address generates an illegal address reset. The SIM verifies that the

CPU is fetching an opcode prior to asserting the ILAD bit in the SIM reset status register (SRSR) and

resetting the MCU. A data fetch from an unmapped address does not generate a reset. The SIM actively

pulls down the RST pin for all internal reset sources.

6.3.2.5 Low-Voltage Inhibit (LVI) Reset

The low-voltage inhibit module (LVI) asserts its output to the SIM when the V

LVI

(RST) is held low while the SIM counter counts out 4096 + 32 CGMXCLK cycles. Thirty-two CGMXCLK

cycles later, the CPU is released from reset to allow the reset vector sequence to occur. The SIM actively

pulls down the RST pin for all internal reset sources.

6.3.2.6 Universal Serial Bus (USB) Reset

The USB module will detect a reset signaled on the bus by the presence of an extended SE0 at the USB

data pins of a device. The MCU seeing a single-ended 0 on its USB data inputs for more than 2.5µs treats

that signal as a reset. After the reset is removed, the device will be in the attached, but not yet addressed

or configured, state (refer to Section 9.1 USB Devices of the Universal Serial Bus Specification Rev. 2.0).

The device must be able to accept the device address via a SET_ADDRESS command (refer to Section

9.4 of the Universal Serial Bus Specification Rev. 2.0) no later than 10ms after the reset is removed.

USB reset can be disabled to generate an internal reset. It can be configured to generate IRQ interrupt.

(See

6.4 SIM Counter

The SIM counter is used by the power-on reset module (POR) and in stop mode recovery to allow the

oscillator time to stabilize before enabling the internal bus (IBUS) clocks. The SIM counter also serves as

a prescaler for the computer operating properly module (COP). The SIM counter overflow supplies the

clock for the COP module. The SIM counter is 12 bits long.

6.4.1 SIM Counter During Power-On Reset

The power-on reset module (POR) detects power applied to the MCU. At power-on, the POR circuit

asserts the signal PORRST. Once the SIM is initialized, it enables the clock generation module (CGM) to

drive the bus clock state machine.

6.4.2 SIM Counter During Stop Mode Recovery

The SIM counter also is used for stop mode recovery. The STOP instruction clears the SIM counter. After

an interrupt, break, or reset, the SIM senses the state of the short stop recovery bit, SSREC, in the mask

Freescale Semiconductor

TRIPF

Chapter 3 Configuration Registers

voltage. The LVI bit in the SIM reset status register (SRSR) is set, and the external reset pin

USB reset is disabled when the USB module is disabled by clearing the

USBEN bit of the USB address register (UADDR).

MC68HC908JW32 Data Sheet, Rev. 6

(CONFIG).)

NOTE

DD

voltage falls to the

SIM Counter

81