CY8C3446LTI-073 Cypress Semiconductor Corp, CY8C3446LTI-073 Datasheet

CY8C3446LTI-073

Specifications of CY8C3446LTI-073

Available stocks

Related parts for CY8C3446LTI-073

CY8C3446LTI-073 Summary of contents

Page 1

... AHB – AMBA (advanced microcontroller bus architecture) high-performance bus, an ARM data transfer bus 2. This feature on select devices only. See Ordering Information 3. GPIOs with opamp outputs are not recommended for use with CapSense. Cypress Semiconductor Corporation Document Number: 001-53304 Rev. *K Programmable System-on-Chip (PSoC ® ...

Page 2

Contents 1. Architectural Overview ..................................................... 3 2. Pinouts ............................................................................... 5 3. Pin Descriptions .............................................................. 10 4. CPU ................................................................................... 11 4.1 8051 CPU ................................................................. 11 4.2 Addressing Modes .................................................... 11 4.3 Instruction Set .......................................................... 12 4.4 DMA and PHUB ....................................................... 16 ...

Page 3

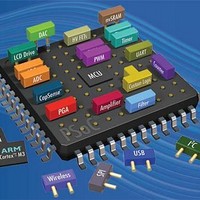

Architectural Overview Introducing the CY8C34 family of ultra low-power, flash Programmable System-on-Chip (PSoC 8-bit PSoC 3 and 32-bit PSoC 5 platform. The CY8C34 family provides configurable blocks of analog, digital, and interconnect circuitry around a CPU subsystem. The combination ...

Page 4

CY8C34 family these blocks can include four 16-bit timer, 2 counter, and PWM blocks slave, master, and multi-master; Full-Speed USB; and Full CAN 2.0b. For more details on the peripherals see the Peripherals” section on page 39 of ...

Page 5

The device provides a PLL to generate system clock frequencies MHz from the IMO, external crystal, or external reference clock. It also contains a separate, very low-power Internal low-speed oscillator (ILO) for the sleep and watchdog timers. ...

Page 6

P2[6] (GPIO) P2[7] (GPIO, TMS, SWDIO) P1[0] (GPIO, TCK, SWDCK) P1[1] (GPIO, Configurable XRES) P1[2] (GPIO, TDO, SWV) P1[3] (GPIO, TDI) P1[4] (GPIO, nTRST) P1[5] Notes 7. Pins are Do Not Use (DNU) on devices without USB. The pin ...

Page 7

P2[6] (GPIO) P2[7] (I2C0: SCL, SIO) P12[4] (I2C0: SDA, SIO) P12[5] Vboost XRES (TMS, SWDIO, GPIO) P1[0] (TCK, SWDCK, GPIO) P1[1] (configurable XRES, GPIO) P1[2] (TDO, SWV, GPIO) P1[3] (TDI, GPIO) P1[4] (nTRST, GPIO) P1[5] Vddio1 Notes 9. Pins ...

Page 8

P2[5] (GPIO) P2[6] (GPIO) P2[7] (I2C0: SCL, SIO) P12[4] (I2C0: SDA, SIO) P12[5] (GPIO) P6[4] (GPIO) P6[5] (GPIO) P6[6] (GPIO) P6[7] Vssb Ind Vboost Vbat Vssd XRES (GPIO) P5[0] (GPIO) P5[1] (GPIO) P5[2] (GPIO) P5[3] (TMS, SWDIO, GPIO) P1[0] ...

Page 9

Figure 2-5 and Figure 2-6 on page 10 show an example schematic and an example PCB layout, for the 100-pin TQFP part, for optimal analog performance on a two-layer board. The two pins labeled Vddd must be connected together. The ...

Page 10

Figure 2-6. Example PCB Layout for 100-pin TQFP Part for Optimal Analog Performance Vssd Plane 3. Pin Descriptions IDAC0, IDAC2 Low resistance output pin for high current DACs (IDAC). OpAmp0out, OpAmp2out High current output of uncommitted opamp Extref0, Extref1 External ...

Page 11

USBIO, D+ Provides D+ connection directly to a USB 2.0 bus. May be used as a digital I/O pin. Pins are Do Not Use (DNU) on devices without USB. USBIO, D– Provides D– connection directly to a USB 2.0 bus. ...

Page 12

Instruction Set The 8051 instruction set is highly optimized for 8-bit handling and Boolean operations. The types of instructions supported include: Arithmetic instructions Logical instructions Data transfer instructions Boolean instructions Program branching instructions Table 4-1. Arithmetic Instructions Mnemonic ADD ...

Page 13

Logical Instructions The logical instructions perform Boolean operations such as AND, OR, XOR on bytes, rotate of accumulator contents, and swap of nibbles in an accumulator. The Boolean operations on the bytes are performed on the bit-by-bit basis. shows ...

Page 14

Data Transfer Instructions The data transfer instructions are of three types: the core RAM, xdata RAM, and the lookup tables. The core RAM transfer includes transfer between any two core RAM locations or SFRs. These instructions can use direct, ...

Page 15

Table 4-4. Boolean Instructions Mnemonic CLR C Clear carry CLR bit Clear direct bit SETB C Set carry SETB bit Set direct bit CPL C Complement carry CPL bit Complement direct bit ANL C, bit AND direct bit to carry ...

Page 16

DMA and PHUB The PHUB and the DMA controller are responsible for data transfer between the CPU and peripherals, and also data transfers between peripherals. The PHUB and DMA also control device configuration during boot. The PHUB consists of: ...

Page 17

Simple DMA In a simple DMA case, a single TD transfers data between a source and sink (peripherals or memory location). The basic timing diagrams of DMA read and write cycles are shown in Reference Manual. ADDRESS Phase CLK ...

Page 18

Multiple I/O interrupt vectors Software can send interrupts Software can clear pending interrupts When an interrupt is pending, the current instruction is completed and the program counter is pushed onto the stack. Code execution then jumps to the program address ...

Page 19

ISR address is read by CPU for branching 8, 9: PEND and POST bits are cleared respectively after receiving the IRA from core 10: IRA bit is cleared after completing the current instruction and starting the instruction execution from ...

Page 20

Table 4-8. Interrupt Vector Table # Fixed Function DMA 0 LVD phub_termout0[0] 1 ECC phub_termout0[1] 2 Reserved phub_termout0[2] 3 Sleep (Pwr Mgr) phub_termout0[3] 4 PICU[0] phub_termout0[4] 5 PICU[1] phub_termout0[5] 6 PICU[2] phub_termout0[6] 7 PICU[3] phub_termout0[7] 8 PICU[4] phub_termout0[8] 9 PICU[5] ...

Page 21

Memory 5.1 Static RAM CY8C34 Static RAM (SRAM) is used for temporary data storage SRAM is provided and can be accessed by the 8051 or the DMA controller. See Memory Map Simultaneous access of ...

Page 22

Nonvolatile Latches (NVLs) PSoC has a 4-byte array of nonvolatile latches (NVLs) that are used to configure the device at reset. The NVL register map is shown in Table 5-2. Table 5-2. Device Configuration NVL Register Map Register Address ...

Page 23

External Memory Interface CY8C34 provides an External Memory Interface (EMIF) for connecting to external memory devices. The connection allows read and write accesses to external memories. The EMIF operates in conjunction with UDBs, I/O ports, and other hardware to ...

Page 24

Figure 5-2. 8051 Internal Data Space 0x00 4 Banks, R0-R7 Each 0x1F 0x20 Bit-Addressable Area 0x2F 0x30 Lower Core RAM Shared with Stack Space (direct and indirect addressing) 0x7F 0x80 Upper Core RAM Shared Special Function Registers with Stack Space ...

Page 25

DSI. Full information on I/O ports is found in I/O System and Routing I/O ports are linked to the CPU through the PHUB and are also available in the SFRs. Using the SFRs allows faster ...

Page 26

Table 6-1. Oscillator Summary Source Fmin Tolerance at Fmin IMO 3 MHz ±1% over voltage and temperature MHzECO 4 MHz Crystal dependent DSI 0 MHz Input dependent PLL 24 MHz Input dependent Doubler 12 MHz Input dependent ILO 1 kHz ...

Page 27

The PLL block provides a mechanism for generating clock frequencies based upon a variety of input sources. The PLL outputs clock frequencies in the range MHz. Its input and feedback dividers supply 4032 discrete ratios to ...

Page 28

Clock Distribution All seven clock sources are inputs to the central clock distribution system. The distribution system is designed to create multiple high precision clocks. These clocks are customized for the design’s requirements and eliminate the common problems found ...

Page 29

Note The two Vccd pins must be connected together with as short a trace as possible. A trace under the device is recommended, as shown in Figure 2-6 on page 10. 6.2.1 Power Modes PSoC 3 devices have four different ...

Page 30

Figure 6-5. Power Mode Transitions Active Manual Sleep Buzz Alternate Active 6.2.1.1 Active Mode Active mode is the primary operating mode of the device. When in active mode, the active configuration template bits control which available resources are enabled or ...

Page 31

The boost converter can be operated in two different modes: active and standby. Active mode is the normal mode of operation where the boost regulator actively generates a regulated output voltage. In standby mode, most boost functions are disabled, thus ...

Page 32

ALVI, DLVI, AHVI – Analog/Digital Low Voltage Interrupt, Analog High Voltage Interrupt Interrupt circuits are available to detect when V go outside a voltage range. For AHVI, V fixed trip level. For ALVI and DLVI, V compared to trip levels ...

Page 33

USBIO features: Full speed USB 2.0 compliant I/O Highest drive strength for general purpose use Input, output, or both for CPU and DMA Digital Input Path PRT[x]CTL PRT[x]DBL_SYNC_IN PRT[x]PS Digital System Input PICU[x]INTTYPE[y] PICU[x]INTSTAT Pin Interrupt Signal PICU[x]INTSTAT Digital Output ...

Page 34

Digital Input Path PRT[x]SIO_HYST_EN PRT[x]SIO_DIFF Reference Level PRT[x]DBL_SYNC_IN PRT[x]PS Digital System Input PICU[x]INTTYPE[y] PICU[x]INTSTAT Pin Interrupt Signal PICU[x]INTSTAT Digital Output Path Reference Level PRT[x]SIO_CFG PRT[x]SLW PRT[x]SYNC_OUT PRT[x]DR Digital System Output PRT[x]BYP PRT[x]DM2 PRT[x]DM1 PRT[x]DM0 Bidirectional Control PRT[x]BIE Digital Input Path ...

Page 35

Drive Modes Each GPIO and SIO pin is individually configurable into one of the eight drive modes listed in Table 6-6. Three configuration bits are used for each pin (DM[2:0]) and set in the PRTxDM[2:0] registers. Figure 6-11 depicts ...

Page 36

Resistive pull-up or resistive pull-down Resistive pull-up or pull-down, respectively, provides a series resistance in one of the data states and strong drive in the other. Pins can be used for digital input and output in these modes. Interfacing to ...

Page 37

LCD Segment Drive This section applies only to GPIO pins. All GPIO pins may be used to generate Segment and Common drive signals for direct glass drive of LCD glass. See the “LCD Direct Drive” page 58 for details. ...

Page 38

Over Voltage Tolerance All I/O pins provide an over voltage tolerance feature at any operating There are no current limitations for the SIO pins as they present a high impedance load to the external circuit where ...

Page 39

Example Peripherals The flexibility of the CY8C34 family’s Universal Digital Blocks (UDBs) and Analog Blocks allow the user to create a wide range of components (peripherals). The most common peripherals were built and characterized by Cypress and are shown ...

Page 40

Document Number: 001-53304 Rev. *K Figure 7-2. PSoC Creator Framework ® PSoC 3: CY8C34 Family Data Sheet Page 40 of 126 [+] Feedback ...

Page 41

Component Catalog Figure 7-3. Component Catalog The component catalog is a repository of reusable design elements that select device functionality and customize your PSoC device populated with an impressive selection of content; from simple primitives such as ...

Page 42

PSoC Creator contains all the tools necessary to complete a design, and then to maintain and extend that design for years to come. All steps of the design flow are carefully integrated and optimized for ease-of-use and to maximize productivity. ...

Page 43

Datapath Module The datapath contains an 8-bit single cycle ALU, with associated compare and condition generation logic. This datapath block is optimized to implement embedded functions, such as timers, counters, integrators, PWMs, PRS, CRC, shifters and dead band generators ...

Page 44

Logical OR Logical XOR Pass, used to pass a value through the ALU to the shift register, mask, or another UDB register Independent of the ALU operation, these functions are available: Shift left Shift right Nibble swap Bitwise OR mask ...

Page 45

UDB state to be read out onto the system bus directly from internal routing. This allows firmware to monitor the state of UDB processing. Each bit of these registers has programmable connections to the routing matrix and routing connections are ...

Page 46

Figure 7-12. Function Mapping Example in a Bank of UDBs 8-Bit 16-Bit Quadrature Decoder Timer PWM UDB UDB UDB UDB UDB UDB 8-Bit SPI I2C Slave 12-Bit SPI UDB UDB UDB Logic ...

Page 47

The synchronization clock is the system clock (see Figure 6-1). Normally all inputs from pins are synchronized as this is required if the CPU interacts with the signal or any signal derived from it. Asynchronous ...

Page 48

CAN Features CAN2.0A/B protocol implementation – ISO 11898 compliant Standard and extended frames with bytes of data per frame Message filter capabilities Remote Transmission Request (RTR) support Programmable bit rate Mbps Listen Only ...

Page 49

USB PSoC includes a dedicated Full-Speed (12 Mbps) USB 2.0 transceiver supporting all four USB transfer types: control, interrupt, bulk, and isochronous. PSoC Creator provides full configuration support. USB interfaces to hosts through two dedicated USBIO pins, which are ...

Page 50

I C features include: Slave and Master, Transmitter, and Receiver operation Byte processing for low CPU overhead Interrupt or polling CPU interface Support for bus speeds Mbps (3.4 Mbps in UDBs 10-bit addressing (10-bit ...

Page 51

GPIO Port Document Number: 001-53304 Rev. *K Figure 8-1. Analog Subsystem Block Diagram DAC Precision Reference DAC SC/CT Block SC/CT Block Com parators ...

Page 52

The PSoC Creator software program provides a user friendly interface to configure the analog connections between the GPIO and various analog resources and connections from one analog resource to another. PSoC Creator also provides component libraries that allow you to ...

Page 53

ExVrefL ExVrefL1 opamp0 opamp2 swinp GPIO swfol swfol P0[4] swinn GPIO P0[5] GPIO * i0 abuf_vref_int P0[6] (1.024V) GPIO * i2 P0[7] cmp0_vref (1.024V) GPIO cmp_muxvn[1:0] P4[2] vref_cmp1 cmp1_vref (0.256V) GPIO bg_vda_res_en Vdda Vdda/2 ...

Page 54

Analog local buses (abus) are routing resources located within the analog subsystem and are used to route signals between different analog blocks. There are eight abus routes in CY8C34, four in the left half (abusl [0:3]) and four in the ...

Page 55

EoC signal is generated. To detect the end of conversion, the system may poll a control register for status or configure the external EoC signal to generate an interrupt ...

Page 56

LUT The CY8C34 family of devices contains four LUTs. The LUT is a two input, one output lookup table that is driven by any one or two of the comparators in the chip. The output of any LUT is ...

Page 57

The PSoC Creator tool offers a user friendly interface, which allows you to easily program the SC/CT blocks. Switch control and clock phase control configuration is done by PSoC Creator so users only need to determine the application use parameters ...

Page 58

The TIA configuration is used for applications where an external sensor's output is current as a function of some type of stimulus such as temperature, light, magnetic flux etc common application, the voltage DAC output can be connected ...

Page 59

CapSense The CapSense system provides a versatile and efficient means for measuring capacitance in applications such as touch sense buttons, sliders, proximity detection, etc. The CapSense system uses a configuration of system resources, including a few hardware functions primarily ...

Page 60

Figure 8-13. Mixer Configuration 850 fF mix sc_clk mix Vin 0 Vref 1 sc_clk 8.11 Sample and Hold The main ...

Page 61

JTAG Interface The IEEE 1149.1 compliant JTAG interface exists on four or five pins (the nTRST pin is optional). The JTAG clock frequency can MHz, or 1/3 of the CPU clock frequency for 8 and ...

Page 62

NVL bits after wafer processing is truly random with no tendency toward The WOL only locks the part after the correct 32-bit key (0×50536F43) is loaded into the NVL's volatile memory, programmed into the ...

Page 63

Electrical Specifications Specifications are valid for –40 °C ≤ T ≤ 85 °C and T A except where noted. The unique flexibility of the PSoC UDBs and analog blocks enable many functions to be implemented in PSoC Creator components, ...

Page 64

Device Level Specifications Specifications are valid for –40 °C ≤ T ≤ 85 °C and T A except where noted. 11.2.1 Device Level Specifications Table 11-2. DC Specifications Parameter Description V Analog supply voltage and input to DDA analog ...

Page 65

Table 11-2. DC Specifications (continued) Parameter Description [22] Sleep Mode CPU = OFF RTC = ON (= ECO32K ON, in low-power mode) Sleep timer = ON (= ILO ON at [23] 1 kHz) WDT = OFF Wake ...

Page 66

Figure 11-1. Active Mode Current vs F Temperature = 25 °C Figure 11-3. Active Mode Current MHz CPU Document Number: 001-53304 Rev 3.3 V, Figure 11-2. Active Mode Current vs Temperature ...

Page 67

Table 11-3. AC Specifications Parameter Description F CPU frequency CPU F Bus frequency BUSCLK Svdd V ramp rate DD T Time from IO_INIT DDD DDA CCD IPOR to I/O ports set to their reset states T ...

Page 68

Power Regulators Specifications are valid for –40 °C ≤ T ≤ 85 °C and T A except where noted. 11.3.1 Digital Core Regulator Table 11-4. Digital Core Regulator DC Specifications Parameter Description V Input voltage DDD V Output voltage ...

Page 69

Inductive Boost Regulator. Table 11-6. Inductive Boost Regulator DC Specifications Unless otherwise specified, operating conditions are µF || 0.1 µF BOOST Parameter Description V Input voltage BAT Includes startup [25, 26] I Load current OUT ...

Page 70

Table 11-7. Inductive Boost Regulator AC Specifications Unless otherwise specified, operating conditions are µF || 0.1 µF. BOOST Parameter Description V Ripple voltage (peak-to-peak) RIPPLE F Switching frequency SW Table 11-8. Recommended External Components for Boost ...

Page 71

Figure 11-10. Efficiency vs I OUT 3.3 V BAT OUT Figure 11-12. Efficiency vs Switching Frequency OUT BAT OUT Document Number: 001-53304 ...

Page 72

Inputs and Outputs Specifications are valid for –40 °C ≤ T ≤ 85 °C and T A except where noted. Unless otherwise specified, all charts and graphs show typical values. 11.1.1 GPIO Table 11-9. GPIO DC Specifications Parameter Description ...

Page 73

Table 11-10. GPIO AC Specifications Parameter Description TriseF Rise time in Fast Strong Mode TfallF Fall time in Fast Strong Mode TriseS Rise time in Slow Strong Mode TfallS Fall time in Slow Strong Mode GPIO output operating frequency 2.7 ...

Page 74

SIO Table 11-11. SIO DC Specifications Parameter Description Vinmax Maximum input voltage Vinref Input voltage reference (Differential input mode) Output voltage reference (Regulated output mode) Voutref Input voltage high threshold V GPIO mode IH [32] Differential input mode Input ...

Page 75

Figure 11-17. SIO Output High Voltage and Current, Unregulated Mode Figure 11-19. SIO Output High Voltage and Current, Regulated Mode Table 11-12. SIO AC Specifications Parameter Description TriseF Rise time in Fast Strong Mode [34] (90/10%) TfallF Fall time in ...

Page 76

Table 11-12. SIO AC Specifications (continued) Parameter Description SIO output operating frequency 2.7 V < V < 5.5 V, Unregulated DDIO output (GPIO) mode, fast strong drive mode 1.71 V < V < 2.7 V, Unregu- DDIO lated output (GPIO) ...

Page 77

Table 11-13. USBIO DC Specifications (continued) Parameter Description Vihgpio Input voltage high, GPIO mode Vilgpio Input voltage low, GPIO mode Vohgpio Output voltage high, GPIO mode Volgpio Output voltage low, GPIO mode Vdi Differential input sensitivity Vcm Differential input common ...

Page 78

Table 11-14. USBIO AC Specifications Parameter Description Tdrate Full-speed data rate average bit rate Tjr1 Receiver data jitter tolerance to next transition Tjr2 Receiver data jitter tolerance to pair transition Tdj1 Driver differential jitter to next transition Tdj2 Driver differential ...

Page 79

XRES Table 11-16. XRES DC Specifications Parameter Description V Input voltage high threshold IH V Input voltage low threshold IL Rpullup Pull-up resistor [35] C Input capacitance IN V Input voltage hysteresis H [35] (Schmitt-Trigger) Idiode Current through protection ...

Page 80

Analog Peripherals Specifications are valid for –40 °C ≤ T ≤ 85 °C and T A except where noted. 11.2.1 Opamp Table 11-18. Opamp DC Specifications Parameter Description V Input offset voltage IOFF Vos Input offset voltage TCVos Input ...

Page 81

Figure 11-27. Opamp Voffset vs Vcommon and Vdda, 25 °C Figure 11-29. Opamp Operating Current vs Vdda and Power Mode Table 11-19. Opamp AC Specifications Parameter Description GBW Gain-bandwidth product SR Slew rate, 20% - 80% e Input noise density ...

Page 82

Figure 11-30. Opamp Noise vs Frequency, Power Mode = High, Vdda = 5V Figure 11-32. Opamp Step Response, Falling Document Number: 001-53304 Rev. *K ® PSoC 3: CY8C34 Family Figure 11-31. Opamp Step Response, Rising Data Sheet Page 82 of ...

Page 83

Delta-sigma ADC Unless otherwise specified, operating conditions are: Operation in continuous sample mode fclk = 6.144 MHz Reference = 1.024 V internal reference bypassed on P3.2 or P0.3 Unless otherwise specified, all charts and graphs show typical values Table ...

Page 84

Table 11-21. Delta-sigma ADC AC Specifications Parameter Description Startup time [38] THD Total harmonic distortion 12-Bit Resolution Mode SR12 Sample rate, continuous, high power BW12 Input bandwidth at max sample rate SINAD12int Signal to noise ratio, 12-bit, internal [38] reference ...

Page 85

Voltage Reference Table 11-23. Voltage Reference Specifications See also ADC external reference specifications in Section Parameter Description V Precision reference voltage REF 11.2.4 Analog Globals Table 11-24. Analog Globals Specifications Parameter Description Rppag Resistance pin-to-pin through [39] analog global ...

Page 86

Current Digital-to-analog Converter (IDAC) See the IDAC component data sheet in PSoC Creator for full electrical specifications and APIs. Unless otherwise specified, all charts and graphs show typical values. Table 11-27. IDAC DC Specifications Parameter Description Resolution I Output ...

Page 87

Table 11-27. IDAC DC Specifications (continued) Parameter Description I Operating current, code = 0 DD Figure 11-34. IDAC INL vs Input Code, Range = 255 µA, Source Mode Document Number: 001-53304 Rev. *K PSoC Conditions Min Slow mode, source mode, ...

Page 88

Figure 11-36. IDAC DNL vs Input Code, Range = 255 µA, Source Mode Figure 11-38. IDAC INL vs Temperature, Range = 255 µA, Fast Mode Document Number: 001-53304 Rev. *K ® PSoC 3: CY8C34 Family Figure 11-37. IDAC DNL vs ...

Page 89

Figure 11-40. IDAC Full Scale Error vs Temperature, Range = 255 µA, Source Mode Figure 11-42. IDAC Operating Current vs Temperature, Range = 255 µA, Code = 0, Source Mode Document Number: 001-53304 Rev. *K ® PSoC 3: CY8C34 Family ...

Page 90

Table 11-28. IDAC AC Specifications Parameter Description F Update rate DAC T Settling time to 0.5 LSB SETTLE Figure 11-44. IDAC Step Response, Codes 0x40 - 0xC0, 255 µA Mode, Source Mode, Fast Mode, Vdda = 5 V Figure 11-46. ...

Page 91

Voltage Digital to Analog Converter (VDAC) See the VDAC component data sheet in PSoC Creator for full electrical specifications and APIs. Unless otherwise specified, all charts and graphs show typical values. Table 11-29. VDAC DC Specifications Parameter Description Resolution ...

Page 92

Figure 11-49. VDAC INL vs Temperature Mode Figure 11-51. VDAC Full Scale Error vs Temperature Mode Figure 11-53. VDAC Operating Current vs Temperature, 1V Mode, Slow Mode Document Number: 001-53304 Rev. *K ® PSoC 3: CY8C34 ...

Page 93

Table 11-30. VDAC AC Specifications Parameter Description F Update rate DAC TsettleP Settling time to 0.1%, step 25% to 75% TsettleN Settling time to 0.1%, step 75% to 25% Figure 11-55. VDAC Step Response, Codes 0x40 - 0xC0 ...

Page 94

Mixer The mixer is created using a SC/CT analog block; see the Mixer component data sheet in PSoC Creator for full electrical specifications and APIs. Table 11-31. Mixer DC Specifications Parameter Description V Input offset voltage OS Quiescent current ...

Page 95

Programmable Gain Amplifier The PGA is created using a SC/CT analog block; see the PGA component data sheet in PSoC Creator for full electrical specifications and APIs. Unless otherwise specified, operating conditions are: Operating temperature = 25 °C for ...

Page 96

Table 11-36. PGA AC Specifications Parameter Description BW1 –3 dB bandwidth SR1 Slew rate e Input noise density n Figure 11-59. Bandwidth vs. Temperature, at Different Gain Settings, Power Mode = High 11.2.11 Temperature Sensor Table 11-37. Temperature Sensor Specifications ...

Page 97

Digital Peripherals Specifications are valid for –40 °C ≤ T ≤ 85 °C and T A except where noted. 11.3.1 Timer The following specifications apply to the Timer/Counter/PWM peripheral in timer mode. Timers can also be implemented in UDBs; ...

Page 98

Pulse Width Modulation The following specifications apply to the Timer/Counter/PWM peripheral, in PWM mode. PWM components can also be implemented in UDBs; for more information, see the PWM component data sheet in PSoC Creator. Table 11-44. PWM DC Specifications ...

Page 99

USB Table 11-50. USB DC Specifications Parameter Description V Device supply for USB operation USB_5 V USB_3.3 V USB_3 I Device supply current in device active USB_Configured mode, bus clock and IMO = 24 MHz I Device supply current ...

Page 100

Memory Specifications are valid for –40 °C ≤ T ≤ 85 °C and T A except where noted. 11.4.1 Flash Table 11-52. Flash DC Specifications Parameter Description Erase and program voltage Table 11-53. Flash AC Specifications Parameter Description T ...

Page 101

Table 11-55. EEPROM AC Specifications Parameter Description T Single row erase/write cycle time WRITE EEPROM data retention time, retention period measured from last erase cycle 11.4.3 Nonvolatile Latches (NVL)) Table 11-56. NVL DC Specifications Parameter Description Erase and program voltage ...

Page 102

External Memory Interface Figure 11-62. Asynchronous Read Cycle Timing EM_ CEn Taddrv EM_ Addr EM_ OEn EM_ WEn EM_ Data Table 11-60. Asynchronous Read Cycle Specifications Parameter Description [45] T EMIF clock period Tcel EM_CEn low time Taddrv EM_CEn ...

Page 103

Figure 11-63. Asynchronous Write Cycle Timing Taddrv EM_ Addr EM_ CEn EM_ WEn EM_ OEn Tdcev EM_ Data Table 11-61. Asynchronous Write Cycle Specifications Parameter Description [46] T EMIF clock period Tcel EM_CEn low time Taddrv EM_CEn low to EM_Addr ...

Page 104

EM_ Clock EM_ CEn EM_ Addr EM_ OEn EM_ Data EM_ ADSCn Table 11-62. Synchronous Read Cycle Specifications Parameter Description [47] T EMIF clock period Tcp/2 EM_Clock pulse high Tceld EM_CEn low to EM_Clock high Tcehd EM_Clock high to EM_CEn ...

Page 105

EM_ Clock EM_ CEn EM_ Addr EM_ WEn EM_ Data EM_ ADSCn Table 11-63. Synchronous Write Cycle Specifications Parameter Description [48] T EMIF clock Period Tcp/2 EM_Clock pulse high Tceld EM_CEn low to EM_Clock high Tcehd EM_Clock high to EM_CEn ...

Page 106

PSoC System Resources Specifications are valid for –40 °C ≤ T ≤ 85 °C and T A except where noted. 11.5.1 POR with Brown Out For brown out detect in regulated mode, V mode. Table 11-64. Precise power-on Reset ...

Page 107

Interrupt Controller Table 11-68. Interrupt Controller AC Specifications Parameter Description Delay from interrupt signal input to ISR code execution from ISR code 11.5.4 JTAG Interface TCK T_TDI_setup TDI TDO T_TMS_setup TMS Table 11-69. JTAG Interface AC Specifications Parameter Description ...

Page 108

SWD Interface SWDCK SWDIO (PSoC 3 reading on SWDIO) SWDIO (PSoC 3 writing to SWDIO) Table 11-70. SWD Interface AC Specifications Parameter Description f_SWDCK SWDCLK frequency T_SWDI_setup SWDIO input setup before SWDCK high T = 1/f_SWDCK max T_SWDI_hold SWDIO ...

Page 109

Clocking Specifications are valid for –40 °C ≤ T ≤ 85 °C and T A except where noted. 11.6.1 32 kHz External Crystal Table 11-72. 32 kHz External Crystal DC Specifications Parameter Description I Operating current CC CL External ...

Page 110

Figure 11-68. IMO Current vs. Frequency Table 11-75. IMO AC Specifications Parameter Description IMO frequency stability (with factory trim) 24 MHz – Non USB mode 24 MHz – USB mode F IMO 12 MHz 6 MHz 3 MHz [54] Startup ...

Page 111

Internal Low-Speed Oscillator Table 11-76. ILO DC Specifications Parameter Description Operating current I CC Leakage current Table 11-77. ILO AC Specifications Parameter Description Startup time, all frequencies ILO frequencies (trimmed) 100 kHz 1 kHz F ILO ILO frequencies (untrimmed) ...

Page 112

External Crystal Oscillator Table 11-78. ECO AC Specifications Parameter Description F Crystal frequency range 11.6.5 External Clock Reference Table 11-79. External Clock Reference AC Specifications Parameter Description External frequency range Input duty cycle range Input edge rate 11.6.6 Phase-Locked ...

Page 113

Ordering Information In addition to the features listed in Table oscillators, flash, ECC, DMA, a fixed function I and more. In addition to these features, the flexible UDBs and analog subsection support a wide range of peripherals. To assist ...

Page 114

... CY8C3446LTI-072 – 12-bit Del-Sig CY8C3446LTI-071 – 12-bit Del-Sig CY8C3446PVI-082 – 12-bit Del-Sig CY8C3446AXI-098 – 12-bit Del-Sig CY8C3446LTI-084 – 12-bit Del-Sig CY8C3446LTI-073 – 12-bit Del-Sig CY8C3446PVI-092 – 12-bit Del-Sig CY8C3446AXI-105 ✔ 12-bit Del-Sig CY8C3446LTI-074 ✔ 12-bit Del-Sig CY8C3446LTI-083 ✔ 12-bit Del-Sig ✔ ...

Page 115

Part Numbering Conventions PSoC 3 devices follow the part numbering convention described here. All fields are single character alphanumeric ( … …, Z) unless stated otherwise. CY8Cabcdefg-xxx a: Architecture 3: PSoC 3 5: PSoC ...

Page 116

Packaging Table 13-1. Package Characteristics Parameter Description T Operating ambient temperature A T Operating junction temperature J Package θJA (48-pin SSOP) Tja Package θJA (48-pin QFN) Tja Package θJA (68-pin QFN) Tja Package θJA (100-pin TQFP) Tja Package θJC ...

Page 117

Figure 13-1. 48-pin (300 mil) SSOP Package Outline 24 25 0.620 0.630 0.088 0.092 0.025 BSC TOP VIEW 7.00±0. PIN 1 DOT LASER MARK NOTES: 1. HATCH AREA IS SOLDERABLE EXPOSED METAL. 2. REFERENCE ...

Page 118

Figure 13-3. 68-pin QFN 8 × 8 with 0.4 mm Pitch Package Outline (Sawn Version) TOP VIEW 8.000±0.100 PIN 1 DOT LASER MARK NOTES: 1. HATCH AREA IS SOLDERABLE EXPOSED METAL. 2. REFERENCE ...

Page 119

Acronyms Table 14-1. Acronyms Used in this Document Acronym Description abus analog local bus ADC analog-to-digital converter AG analog global AHB AMBA (advanced microcontroller bus archi- tecture) high-performance bus, an ARM data transfer bus ALU arithmetic logic unit AMUXBUS ...

Page 120

Table 14-1. Acronyms Used in this Document (continued) Acronym Description PHUB peripheral hub PHY physical layer PICU port interrupt control unit PLA programmable logic array PLD programmable logic device, see also PAL PLL phase-locked loop PMDD package material declaration data ...

Page 121

Document Conventions 16.1 Units of Measure Table 16-1. Units of Measure Symbol Unit of Measure °C degrees Celsius dB decibels fF femtofarads Hz hertz KB 1024 bytes kbps kilobits per second Khr kilohours kHz kilohertz kΩ kilohms ksps kilosamples ...

Page 122

Revision History ® Description Title: PSoC 3: CY8C34 Family Data Sheet Programmable System-on-Chip (PSoC Document Number: 001-53304 Submission Rev. ECN No. Date ** 2714270 06/03/09 *A 2758970 09/02/09 *B 2824546 12/09/09 *C 2873322 02/04/10 Document Number: 001-53304 Rev. *K ...

Page 123

Description Title: PSoC 3: CY8C34 Family Data Sheet Programmable System-on-Chip (PSoC Document Number: 001-53304 *D 2903576 04/01/10 Document Number: 001-53304 Rev. *K MKEA Updated Vb pin in PCB Schematic Updated Tstartup parameter in AC Specifications table Added Load regulation ...

Page 124

Description Title: PSoC 3: CY8C34 Family Data Sheet Programmable System-on-Chip (PSoC Document Number: 001-53304 *E 2938381 05/27/10 *F 2958674 06/22/10 *G 2989685 08/04/10 *H 3078568 11/04/10 *I 3107314 12/10/2010 *J 3179219 02/22/2011 Document Number: 001-53304 Rev. *K MKEA Replaced ...

Page 125

Description Title: PSoC 3: CY8C34 Family Data Sheet Programmable System-on-Chip (PSoC Document Number: 001-53304 *K 3200146 03/28/2011 Document Number: 001-53304 Rev. *K MKEA Removed Preliminary status from the data sheet. Updated JTAG ID Deleted Cin_G1, ADC input capacitance from ...

Page 126

... Cypress against all charges. Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement ...