CY8C3446LTI-073 Cypress Semiconductor Corp, CY8C3446LTI-073 Datasheet - Page 30

CY8C3446LTI-073

Manufacturer Part Number

CY8C3446LTI-073

Description

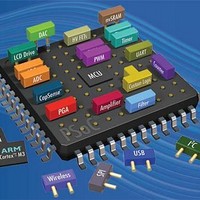

IC MCU 8BIT 64KB FLASH 48QFN

Manufacturer

Cypress Semiconductor Corp

Series

PSOC™ 3 CY8C34xxr

Specifications of CY8C3446LTI-073

Package / Case

*

Voltage - Supply (vcc/vdd)

1.71 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Speed

50MHz

Number Of I /o

25

Eeprom Size

2K x 8

Core Processor

8051

Program Memory Type

FLASH

Ram Size

8K x 8

Program Memory Size

64KB (64K x 8)

Data Converters

A/D 2x12b, D/A 2x8b

Oscillator Type

Internal

Peripherals

CapSense, DMA, POR, PWM, WDT

Connectivity

EBI/EMI, I²C, LIN, SPI, UART/USART, USB

Core Size

8-Bit

Operating Temperature (min)

-40C

Operating Temperature (max)

85C

Technology

CMOS

Processing Unit

Microcontroller

Operating Supply Voltage (min)

1.8V

Operating Supply Voltage (typ)

2.5/3.3/5V

Operating Supply Voltage (max)

5.5V

Package Type

QFN EP

Screening Level

Industrial

Pin Count

48

Mounting

Surface Mount

Rad Hardened

No

Processor Series

CY8C34

Core

8051

Data Bus Width

32 bit

Data Ram Size

8 KB

Interface Type

I2C, SPI, UART, USB

Maximum Clock Frequency

50 MHz

Number Of Programmable I/os

28 to 72

Number Of Timers

4

Operating Supply Voltage

1.71 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Controller Family/series

(8051) PSOC 3

No. Of I/o's

25

Eeprom Memory Size

2KB

Ram Memory Size

8KB

Cpu Speed

50MHz

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Compliant, Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

CY8C3446LTI-073

Manufacturer:

CYPRESS/赛普拉斯

Quantity:

20 000

Figure 6-5. Power Mode Transitions

6.2.1.1 Active Mode

Active mode is the primary operating mode of the device. When

in active mode, the active configuration template bits control

which available resources are enabled or disabled. When a

resource is disabled, the digital clocks are gated, analog bias

currents are disabled, and leakage currents are reduced as

appropriate. User firmware can dynamically control subsystem

power by setting and clearing bits in the active configuration

template. The CPU can disable itself, in which case the CPU is

automatically reenabled at the next wakeup event.

When a wakeup event occurs, the global mode is always

returned to active, and the CPU is automatically enabled,

regardless of its template settings. Active mode is the default

global power mode upon boot.

6.2.1.2 Alternate Active Mode

Alternate Active mode is very similar to Active mode. In alternate

active mode, fewer subsystems are enabled, to reduce power

consumption. One possible configuration is to turn off the CPU

and flash, and run peripherals at full speed.

6.2.1.3 Sleep Mode

Sleep mode reduces power consumption when a resume time of

15 µs is acceptable. The wake time is used to ensure that the

regulator outputs are stable enough to directly enter active

mode.

6.2.1.4 Hibernate Mode

In hibernate mode nearly all of the internal functions are

disabled. Internal voltages are reduced to the minimal level to

keep vital systems alive. Configuration state is preserved in

hibernate mode and SRAM memory is retained. GPIOs

configured as digital outputs maintain their previous values and

external GPIO pin interrupt settings are preserved. The device

can only return from hibernate mode in response to an external

I/O interrupt. The resume time from hibernate mode is less than

100 µs.

6.2.1.5 Wakeup Events

Wakeup events are configurable and can come from an interrupt

or device reset. A wakeup event restores the system to active

mode. Firmware enabled interrupt sources include internally

generated interrupts, power supervisor, central timewheel, and

Document Number: 001-53304 Rev. *K

Manual

Buzz

Alternate

Active

Active

Sleep

Hibernate

I/O interrupts. Internal interrupt sources can come from a variety

of peripherals, such as analog comparators and UDBs. The

central timewheel provides periodic interrupts to allow the

system to wake up, poll peripherals, or perform real-time

functions. Reset event sources include the external reset I/O pin

(XRES), WDT, and Precision Reset (PRES).

6.2.2 Boost Converter

Applications that use a supply voltage of less than 1.71 V, such

as solar or single cell battery supplies, may use the on-chip boost

converter. The boost converter may also be used in any system

that requires a higher operating voltage than the supply provides.

For instance, this includes driving 5.0 V LCD glass in a 3.3 V

system. The boost converter accepts an input voltage as low as

0.5 V. With one low cost inductor it produces a selectable output

voltage sourcing enough current to operate the PSoC and other

on-board components.

The boost converter accepts an input voltage from 0.5 V to 5.5 V

(Vbat), and can start up with Vbat as low as 0.5 V. The converter

provides a user configurable output voltage of 1.8 to 5.0 V

(Vboost). Vbat is typically less than Vboost; if Vbat is greater than

or equal to Vboost, then V

block can deliver up to 50 mA (I

configuration.

Four pins are associated with the boost converter: Vbat, Vssb,

Vboost, and Ind. The boosted output voltage is sensed at the

Vboost pin and must be connected directly to the chip’s supply

inputs. An inductor is connected between the Vbat and Ind pins.

You can optimize the inductor value to increase the boost

converter efficiency based on input voltage, output voltage,

current and switching frequency. The external Schottky diode

shown in

3.6 V.

Figure 6-6. Application for Boost Converter

The switching frequency can be set to 100 kHz, 400 kHz, 2 MHz,

or 32 kHz to optimize efficiency and component cost. The

100 kHz, 400 kHz, and 2 MHz switching frequencies are

generated using oscillators internal to the boost converter block.

When the 32-kHz switching frequency is selected, the clock is

derived from a 32 kHz external crystal oscillator. The 32-kHz

external clock is primarily intended for boost standby mode.

At 2 MHz the Vboost output is limited to 2 × Vbat, and at 400 kHz

Vboost is limited to 4 × Vbat.

Vboost > 3.6 V

Schottky Diode

Only required

Optional

Figure 6-6

10 µH

22 µF

SMP

is required only in cases when Vboost >

Vbat

Vssb

PSoC

Vboost

Ind

BOOST

Vdda Vddd

PSoC

®

BOOST

will be the same as Vbat. The

3: CY8C34 Family

Vssa

Vssd

Vddio

) depending on

22 µF 0. 1 µF

Data Sheet

Page 30 of 126

[+] Feedback