CY8C3446LTI-073 Cypress Semiconductor Corp, CY8C3446LTI-073 Datasheet - Page 28

CY8C3446LTI-073

Manufacturer Part Number

CY8C3446LTI-073

Description

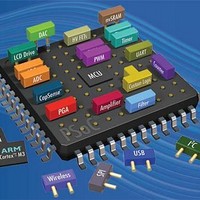

IC MCU 8BIT 64KB FLASH 48QFN

Manufacturer

Cypress Semiconductor Corp

Series

PSOC™ 3 CY8C34xxr

Specifications of CY8C3446LTI-073

Package / Case

*

Voltage - Supply (vcc/vdd)

1.71 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Speed

50MHz

Number Of I /o

25

Eeprom Size

2K x 8

Core Processor

8051

Program Memory Type

FLASH

Ram Size

8K x 8

Program Memory Size

64KB (64K x 8)

Data Converters

A/D 2x12b, D/A 2x8b

Oscillator Type

Internal

Peripherals

CapSense, DMA, POR, PWM, WDT

Connectivity

EBI/EMI, I²C, LIN, SPI, UART/USART, USB

Core Size

8-Bit

Operating Temperature (min)

-40C

Operating Temperature (max)

85C

Technology

CMOS

Processing Unit

Microcontroller

Operating Supply Voltage (min)

1.8V

Operating Supply Voltage (typ)

2.5/3.3/5V

Operating Supply Voltage (max)

5.5V

Package Type

QFN EP

Screening Level

Industrial

Pin Count

48

Mounting

Surface Mount

Rad Hardened

No

Processor Series

CY8C34

Core

8051

Data Bus Width

32 bit

Data Ram Size

8 KB

Interface Type

I2C, SPI, UART, USB

Maximum Clock Frequency

50 MHz

Number Of Programmable I/os

28 to 72

Number Of Timers

4

Operating Supply Voltage

1.71 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Controller Family/series

(8051) PSOC 3

No. Of I/o's

25

Eeprom Memory Size

2KB

Ram Memory Size

8KB

Cpu Speed

50MHz

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Compliant, Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

CY8C3446LTI-073

Manufacturer:

CYPRESS/赛普拉斯

Quantity:

20 000

6.1.3 Clock Distribution

All seven clock sources are inputs to the central clock distribution

system. The distribution system is designed to create multiple

high precision clocks. These clocks are customized for the

design’s requirements and eliminate the common problems

found with limited resolution prescalers attached to peripherals.

The clock distribution system generates several types of clock

trees.

Document Number: 001-53304 Rev. *K

The system clock is used to select and supply the fastest clock

in the system for general system clock requirements and clock

synchronization of the PSoC device.

Bus Clock 16-bit divider uses the system clock to generate the

system's bus clock used for data transfers. Bus clock is the

source clock for the CPU clock divider.

Eight fully programmable 16-bit clock dividers generate digital

system clocks for general use in the digital system, as

configured by the design’s requirements. Digital system clocks

can generate custom clocks derived from any of the seven

clock sources for any purpose. Examples include baud rate

generators, accurate PWM periods, and timer clocks, and

many others. If more than eight digital clock dividers are

required, the Universal Digital Blocks (UDBs) and fixed function

Timer/Counter/PWMs can also generate clocks.

Four 16-bit clock dividers generate clocks for the analog system

components that require clocking, such as ADC and mixers.

The analog clock dividers include skew control to ensure that

critical analog events do not occur simultaneously with digital

switching events. This is done to reduce analog system noise.

Vddio1

Vddio2

Vssd

0.1µF

0.1µF

I / O Supply

I/O Supply

Domain

Digital

Figure 6-4. PSoC Power System

1 µF

Regulators

Digital

0.1 µF

Vddd

Vddd

Each clock divider consists of an 8-input multiplexer, a 16-bit

clock divider (divide by 2 and higher) that generates ~50 percent

duty cycle clocks, system clock resynchronization logic, and

deglitch logic. The outputs from each digital clock tree can be

routed into the digital system interconnect and then brought back

into the clock system as an input, allowing clock chaining of up

to 32 bits.

6.1.4 USB Clock Domain

The USB clock domain is unique in that it operates largely

asynchronously from the main clock network. The USB logic

contains a synchronous bus interface to the chip, while running

on an asynchronous clock to process USB data. The USB logic

requires a 48 MHz frequency. This frequency can be generated

from different sources, including DSI clock at 48 MHz or doubled

value of 24 MHz from internal oscillator, DSI signal, or crystal

oscillator.

6.2 Power System

The power system consists of separate analog, digital, and I/O

supply pins, labeled Vdda, Vddd, and Vddiox, respectively. It

also includes two internal 1.8 V regulators that provide the digital

(Vccd) and analog (Vcca) supplies for the internal core logic. The

output pins of the regulators (Vccd and Vcca) and the Vddio pins

must have capacitors connected as shown in

two Vccd pins must be shorted together, with as short a trace as

possible, and connected to a 1 µF ±10 percent X5R capacitor.

The power system also contains a sleep regulator, an I

regulator, and a hibernate regulator.

0.1 µF

Regulator

I/O Supply

Regulator

Regulator

Analog

Regulator

Hibernate

Domain

Analog

Sleep

I2C

I/O Supply

0.1 µF

Vddio0

Vdda

Vcca

PSoC

Vssa

Vddio3

Vddio0

®

1 µF

0.1 µF

Vdda

3: CY8C34 Family

0.1µF

.

Data Sheet

Figure

Page 28 of 126

6-4. The

2

C

[+] Feedback