CY8C3446LTI-073 Cypress Semiconductor Corp, CY8C3446LTI-073 Datasheet - Page 18

CY8C3446LTI-073

Manufacturer Part Number

CY8C3446LTI-073

Description

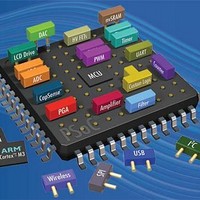

IC MCU 8BIT 64KB FLASH 48QFN

Manufacturer

Cypress Semiconductor Corp

Series

PSOC™ 3 CY8C34xxr

Specifications of CY8C3446LTI-073

Package / Case

*

Voltage - Supply (vcc/vdd)

1.71 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Speed

50MHz

Number Of I /o

25

Eeprom Size

2K x 8

Core Processor

8051

Program Memory Type

FLASH

Ram Size

8K x 8

Program Memory Size

64KB (64K x 8)

Data Converters

A/D 2x12b, D/A 2x8b

Oscillator Type

Internal

Peripherals

CapSense, DMA, POR, PWM, WDT

Connectivity

EBI/EMI, I²C, LIN, SPI, UART/USART, USB

Core Size

8-Bit

Operating Temperature (min)

-40C

Operating Temperature (max)

85C

Technology

CMOS

Processing Unit

Microcontroller

Operating Supply Voltage (min)

1.8V

Operating Supply Voltage (typ)

2.5/3.3/5V

Operating Supply Voltage (max)

5.5V

Package Type

QFN EP

Screening Level

Industrial

Pin Count

48

Mounting

Surface Mount

Rad Hardened

No

Processor Series

CY8C34

Core

8051

Data Bus Width

32 bit

Data Ram Size

8 KB

Interface Type

I2C, SPI, UART, USB

Maximum Clock Frequency

50 MHz

Number Of Programmable I/os

28 to 72

Number Of Timers

4

Operating Supply Voltage

1.71 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Controller Family/series

(8051) PSOC 3

No. Of I/o's

25

Eeprom Memory Size

2KB

Ram Memory Size

8KB

Cpu Speed

50MHz

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Compliant, Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

CY8C3446LTI-073

Manufacturer:

CYPRESS/赛普拉斯

Quantity:

20 000

Document Number: 001-53304 Rev. *K

When an interrupt is pending, the current instruction is completed and the program

counter is pushed onto the stack. Code execution then jumps to the program address

provided by the vector. After the ISR is completed, a RETI instruction is executed

and returns execution to the instruction following the previously interrupted

instruction. To do this the RETI instruction pops the program counter from the stack.

If the same priority level is assigned to two or more interrupts, the interrupt with the

lower vector number is executed first. Each interrupt vector may choose from three

Notes

1: Interrupt triggered asynchronous to the clock

2: The PEND bit is set on next active clock edge to indicate the interrupt arrival

3: POST bit is set following the PEND bit

4: Interrupt request and the interrupt number sent to CPU core after evaluation priority (Takes 3 clocks)

5: ISR address is posted to CPU core for branching

6: CPU acknowledges the interrupt request

Multiple I/O interrupt vectors

Software can send interrupts

Software can clear pending interrupts

ACTIVE_INT_NUM

INT_VECT_ADDR

INT_INPUT

PEND

POST

(#10)

IRA

CLK

IRQ

IRC

1

Interrupt generation and posting to CPU

Arrival of new Interrupt

2

Pend bit is set on next system clock active edge

NA

NA

3

Interrupt is posted to ascertain the priority

4

Interrupt request sent to core for processing

5

CPU Response

address is posted to core

The active interrupt ISR

Figure 4-2. Interrupt Processing Timing Diagram

0x0010

6

Int. State

number is posted to core

Clear

The active interrupt

7

IRQ cleared after receiving IRA

8

Completing current instruction and branching to vector address

interrupt sources: Fixed Function, DMA, and UDB. The fixed function interrupts are

direct connections to the most common interrupt sources and provide the lowest

resource cost connection. The DMA interrupt sources provide direct connections to

the two DMA interrupt sources provided per DMA channel. The third interrupt source

for vectors is from the UDB digital routing array. This allows any digital signal

available to the UDB array to be used as an interrupt source. Fixed function interrupts

and all interrupt sources may be routed to any interrupt vector using the UDB

interrupt source connections.

Figure 4-2

Figure 4-3

9

POST and PEND bits cleared after IRQ is sleared

on page 18 represents typical flow of events when an interrupt triggered.

on page 19 shows the interrupt structure and priority polling.

NA

10

PSoC

Complete ISR and return

®

S

S

S

S

S

S

S

S

S

S

S

3: CY8C34 Family

11

0x0000

Data Sheet

Page 18 of 126

TIME

[+] Feedback