CY8C3446LTI-073 Cypress Semiconductor Corp, CY8C3446LTI-073 Datasheet - Page 61

CY8C3446LTI-073

Manufacturer Part Number

CY8C3446LTI-073

Description

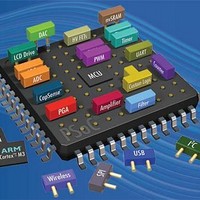

IC MCU 8BIT 64KB FLASH 48QFN

Manufacturer

Cypress Semiconductor Corp

Series

PSOC™ 3 CY8C34xxr

Specifications of CY8C3446LTI-073

Package / Case

*

Voltage - Supply (vcc/vdd)

1.71 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Speed

50MHz

Number Of I /o

25

Eeprom Size

2K x 8

Core Processor

8051

Program Memory Type

FLASH

Ram Size

8K x 8

Program Memory Size

64KB (64K x 8)

Data Converters

A/D 2x12b, D/A 2x8b

Oscillator Type

Internal

Peripherals

CapSense, DMA, POR, PWM, WDT

Connectivity

EBI/EMI, I²C, LIN, SPI, UART/USART, USB

Core Size

8-Bit

Operating Temperature (min)

-40C

Operating Temperature (max)

85C

Technology

CMOS

Processing Unit

Microcontroller

Operating Supply Voltage (min)

1.8V

Operating Supply Voltage (typ)

2.5/3.3/5V

Operating Supply Voltage (max)

5.5V

Package Type

QFN EP

Screening Level

Industrial

Pin Count

48

Mounting

Surface Mount

Rad Hardened

No

Processor Series

CY8C34

Core

8051

Data Bus Width

32 bit

Data Ram Size

8 KB

Interface Type

I2C, SPI, UART, USB

Maximum Clock Frequency

50 MHz

Number Of Programmable I/os

28 to 72

Number Of Timers

4

Operating Supply Voltage

1.71 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Controller Family/series

(8051) PSOC 3

No. Of I/o's

25

Eeprom Memory Size

2KB

Ram Memory Size

8KB

Cpu Speed

50MHz

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Compliant, Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

CY8C3446LTI-073

Manufacturer:

CYPRESS/赛普拉斯

Quantity:

20 000

9.1 JTAG Interface

The IEEE 1149.1 compliant JTAG interface exists on four or five

pins (the nTRST pin is optional). The JTAG clock frequency can

be up to 8 MHz, or 1/3 of the CPU clock frequency for 8 and 16-bit

transfers, or 1/5 of the CPU clock frequency for 32-bit transfers,

whichever is least. By default, the JTAG pins are enabled on new

devices but the JTAG interface can be disabled, allowing these

pins to be used as General Purpose I/O (GPIO) instead. The

JTAG interface is used for programming the flash memory,

debugging, I/O scan chains, and JTAG device chaining.

9.2 Serial Wire Debug Interface

The SWD interface is the preferred alternative to the JTAG

interface. It requires only two pins instead of the four or five

needed by JTAG. SWD provides all of the programming and

debugging features of JTAG at the same speed. SWD does not

provide access to scan chains or device chaining. The SWD

clock frequency can be up to 1/3 of the CPU clock frequency.

SWD uses two pins, either two of the JTAG pins (TMS and TCK)

or the USBIO D+ and D– pins. The USBIO pins are useful for in

system programming of USB solutions that would otherwise

require a separate programming connector. One pin is used for

the data clock and the other is used for data input and output.

SWD can be enabled on only one of the pin pairs at a time. This

only happens if, within 8 µs (key window) after reset, that pin pair

(JTAG or USB) receives a predetermined sequence of 1s and 0s.

SWD is used for debugging or for programming the flash

memory.

The SWD interface can be enabled from the JTAG interface or

disabled, allowing its pins to be used as GPIO. Unlike JTAG, the

SWD interface can always be reacquired on any device during

the key window. It can then be used to reenable the JTAG

interface, if desired. When using SWD or JTAG pins as standard

GPIO, make sure that the GPIO functionality and PCB circuits do

not interfere with SWD or JTAG use.

9.3 Debug Features

Using the JTAG or SWD interface, the CY8C34 supports the

following debug features:

Document Number: 001-53304 Rev. *K

Halt and single-step the CPU

View and change CPU and peripheral registers, and RAM

addresses

Eight program address breakpoints

One memory access breakpoint—break on reading or writing

any memory address and data value

Break on a sequence of breakpoints (non recursive)

Debugging at the full speed of the CPU

Debug operations are possible while the device is reset, or in

low-power modes

Compatible with PSoC Creator and MiniProg3 programmer and

debugger

Standard JTAG programming and debugging interfaces make

CY8C34 compatible with other popular third-party tools (for

example, ARM / Keil)

9.4 Trace Features

The CY8C34 supports the following trace features when using

JTAG or SWD:

9.5 Single Wire Viewer Interface

The SWV interface is closely associated with SWD but can also

be used independently. SWV data is output on the JTAG

interface’s TDO pin. If using SWV, you must configure the device

for SWD, not JTAG. SWV is not supported with the JTAG

interface.

SWV is ideal for application debug where it is helpful for the

firmware to output data similar to 'printf' debugging on PCs. The

SWV is ideal for data monitoring, because it requires only a

single pin and can output data in standard UART format or

Manchester encoded format. For example, it can be used to tune

a PID control loop in which the output and graphing of the three

error terms greatly simplifies coefficient tuning.

The following features are supported in SWV:

9.6 Programming Features

The JTAG and SWD interfaces provide full programming

support. The entire device can be erased, programmed, and

verified. You can increase flash protection levels to protect

firmware IP. Flash protection can only be reset after a full device

erase. Individual flash blocks can be erased, programmed, and

verified, if block security settings permit.

9.7 Device Security

PSoC 3 offers an advanced security feature called device

security, which permanently disables all test, programming, and

debug ports, protecting your application from external access.

The device security is activated by programming a 32-bit key

(0x50536F43) to a Write Once Latch (WOL).

The Write Once Latch is a type of nonvolatile latch (NVL). The

cell itself is an NVL with additional logic wrapped around it. Each

WOL device contains four bytes (32 bits) of data. The wrapper

outputs a ‘1’ if a super-majority (28 of 32) of its bits match a

pre-determined pattern (0×50536F43); it outputs a ‘0’ if this

majority is not reached. When the output is 1, the Write Once NV

latch locks the part out of Debug and Test modes; it also

permanently gates off the ability to erase or alter the contents of

the latch. Matching all bits is intentionally not required, so that

single (or few) bit failures do not deassert the WOL output. The

Trace the 8051 program counter (PC), accumulator register

(ACC), and one SFR / 8051 core RAM register

Trace depth up to 1000 instructions if all registers are traced,

or 2000 instructions if only the PC is traced (on devices that

include trace memory)

Program address trigger to start tracing

Trace windowing, that is, only trace when the PC is within a

given range

Two modes for handling trace buffer full: continuous (overwriting

the oldest trace data) or break when trace buffer is full

32 virtual channels, each 32 bits long

Simple, efficient packing and serializing protocol

Supports standard UART format (N81)

PSoC

®

3: CY8C34 Family

Data Sheet

Page 61 of 126

[+] Feedback