CY7C68053-56BAXIT Cypress Semiconductor Corp, CY7C68053-56BAXIT Datasheet - Page 39

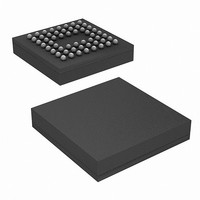

CY7C68053-56BAXIT

Manufacturer Part Number

CY7C68053-56BAXIT

Description

CY7C68053-56BAXIT

Manufacturer

Cypress Semiconductor Corp

Series

MoBL-USB™r

Datasheet

1.CY7C68053-56BAXI.pdf

(42 pages)

Specifications of CY7C68053-56BAXIT

Applications

USB Microcontroller

Core Processor

8051

Program Memory Type

ROMless

Controller Series

CY7C680xx

Ram Size

16K x 8

Interface

I²C, USB

Number Of I /o

56

Voltage - Supply

1.71 V ~ 1.89 V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

56-VFBGA

Processor Series

CY7C68xx

Core

8051

Data Bus Width

8 bit

Data Ram Size

16 KB

Interface Type

I2C

Maximum Clock Frequency

48 MHz

Number Of Programmable I/os

24

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

CY3687 - KIT DEV MOBL-USB FX2LP18

Lead Free Status / Rohs Status

Details

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY7C68053-56BAXIT

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

12. PCB Layout Recommendations

The following recommendations must be followed to ensure

reliable high performance operation.

■

■

■

■

■

Document # 001-06120 Rev *J

At least a four-layer impedance controlled board is required to

maintain signal quality.

Specify impedance targets (ask your board vendor what they

can achieve).

To control impedance, maintain trace widths and trace spacing

to within specifications.

Minimize stubs to minimize reflected signals.

Connections between the USB connector shell and signal

ground must be done near the USB connector.

■

■

■

■

■

Bypass or flyback caps on VBus, near connector, are

recommended.

DPLUS and DMINUS trace lengths must be kept within 2 mm

of each other in length, with preferred length of 20 to 30 mm.

Maintain a solid ground plane under the DPLUS and DMINUS

traces. Do not allow the plane to be split under these traces.

It is preferable to have no vias placed on the DPLUS or

DMINUS trace routing.

Isolate the DPLUS and DMINUS traces from all other signal

traces by no less than 10 mm.

CY7C68053

Page 39 of 42

[+] Feedback