EPM7256EGI192-20 Altera, EPM7256EGI192-20 Datasheet - Page 17

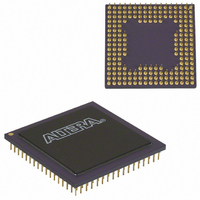

EPM7256EGI192-20

Manufacturer Part Number

EPM7256EGI192-20

Description

IC MAX 7000 CPLD 256 192-PGA

Manufacturer

Altera

Series

MAX® 7000r

Datasheet

1.EPM7064STC44-10.pdf

(66 pages)

Specifications of EPM7256EGI192-20

Programmable Type

In System Programmable

Delay Time Tpd(1) Max

20.0ns

Voltage Supply - Internal

4.5 V ~ 5.5 V

Number Of Logic Elements/blocks

16

Number Of Macrocells

256

Number Of Gates

5000

Number Of I /o

164

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

192-PGA

Voltage

5V

Memory Type

EEPROM

Number Of Logic Elements/cells

16

Family Name

MAX 7000

# Macrocells

256

Number Of Usable Gates

5000

Frequency (max)

83.33MHz

Propagation Delay Time

20ns

Number Of Logic Blocks/elements

16

# I/os (max)

164

Operating Supply Voltage (typ)

5V

In System Programmable

Yes

Operating Supply Voltage (min)

4.5V

Operating Supply Voltage (max)

5.5V

Operating Temp Range

-40C to 85C

Operating Temperature Classification

Industrial

Mounting

Through Hole

Pin Count

192

Package Type

CPGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Features

-

Lead Free Status / Rohs Status

Compliant

Other names

544-2356

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

EPM7256EGI192-20

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

Altera Corporation

f

For more information on using the Jam language, refer to AN 122: Using

Jam STAPL for ISP & ICR via an Embedded Processor.

The ISP circuitry in MAX 7000S devices is compatible with IEEE Std. 1532

specification. The IEEE Std. 1532 is a standard developed to allow

concurrent ISP between multiple PLD vendors.

Programming Sequence

During in-system programming, instructions, addresses, and data are

shifted into the MAX 7000S device through the TDI input pin. Data is

shifted out through the TDO output pin and compared against the

expected data.

Programming a pattern into the device requires the following six ISP

stages. A stand-alone verification of a programmed pattern involves only

stages 1, 2, 5, and 6.

1.

2.

3.

4.

5.

6.

Enter ISP. The enter ISP stage ensures that the I/O pins transition

smoothly from user mode to ISP mode. The enter ISP stage requires

1 ms.

Check ID. Before any program or verify process, the silicon ID is

checked. The time required to read this silicon ID is relatively small

compared to the overall programming time.

Bulk Erase. Erasing the device in-system involves shifting in the

instructions to erase the device and applying one erase pulse of

100 ms.

Program. Programming the device in-system involves shifting in the

address and data and then applying the programming pulse to

program the EEPROM cells. This process is repeated for each

EEPROM address.

Verify. Verifying an Altera device in-system involves shifting in

addresses, applying the read pulse to verify the EEPROM cells, and

shifting out the data for comparison. This process is repeated for

each EEPROM address.

Exit ISP. An exit ISP stage ensures that the I/O pins transition

smoothly from ISP mode to user mode. The exit ISP stage requires

1 ms.

MAX 7000 Programmable Logic Device Family Data Sheet

17