EPM7256EGI192-20 Altera, EPM7256EGI192-20 Datasheet - Page 64

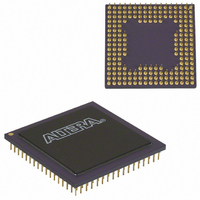

EPM7256EGI192-20

Manufacturer Part Number

EPM7256EGI192-20

Description

IC MAX 7000 CPLD 256 192-PGA

Manufacturer

Altera

Series

MAX® 7000r

Datasheet

1.EPM7064STC44-10.pdf

(66 pages)

Specifications of EPM7256EGI192-20

Programmable Type

In System Programmable

Delay Time Tpd(1) Max

20.0ns

Voltage Supply - Internal

4.5 V ~ 5.5 V

Number Of Logic Elements/blocks

16

Number Of Macrocells

256

Number Of Gates

5000

Number Of I /o

164

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

192-PGA

Voltage

5V

Memory Type

EEPROM

Number Of Logic Elements/cells

16

Family Name

MAX 7000

# Macrocells

256

Number Of Usable Gates

5000

Frequency (max)

83.33MHz

Propagation Delay Time

20ns

Number Of Logic Blocks/elements

16

# I/os (max)

164

Operating Supply Voltage (typ)

5V

In System Programmable

Yes

Operating Supply Voltage (min)

4.5V

Operating Supply Voltage (max)

5.5V

Operating Temp Range

-40C to 85C

Operating Temperature Classification

Industrial

Mounting

Through Hole

Pin Count

192

Package Type

CPGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Features

-

Lead Free Status / Rohs Status

Compliant

Other names

544-2356

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

EPM7256EGI192-20

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

MAX 7000 Programmable Logic Device Family Data Sheet

Revision

History

64

The information contained in the MAX 7000 Programmable Logic Device

Family Data Sheet version 6.7 supersedes information published in

previous versions. The following changes were made in the MAX 7000

Programmable Logic Device Family Data Sheet version 6.7:

Version 6.7

The following changes were made in the MAX 7000 Programmable Logic

Device Family Data Sheet version 6.7:

■

Version 6.6

The following changes were made in the MAX 7000 Programmable Logic

Device Family Data Sheet version 6.6:

■

■

Version 6.5

The following changes were made in the MAX 7000 Programmable Logic

Device Family Data Sheet version 6.5:

■

Version 6.4

The following changes were made in the MAX 7000 Programmable Logic

Device Family Data Sheet version 6.4:

■

Version 6.3

The following changes were made in the MAX 7000 Programmable Logic

Device Family Data Sheet version 6.3:

■

Reference to AN 88: Using the Jam Language for ISP & ICR via an

Embedded Processor has been replaced by AN 122: Using Jam STAPL for

ISP & ICR via an Embedded Processor.

Added

Added

“Programming Times” section on page 18.

Updated text on

Added

Updated the

Only)” section on page

Tables 6

“Programming Sequence” section on page 17

Note (5)

“Open-Drain Output Option (MAX 7000S Devices

through 8.

on

page

page

16.

20.

28.

Altera Corporation

and