EPM7256EGI192-20 Altera, EPM7256EGI192-20 Datasheet - Page 52

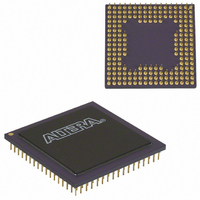

EPM7256EGI192-20

Manufacturer Part Number

EPM7256EGI192-20

Description

IC MAX 7000 CPLD 256 192-PGA

Manufacturer

Altera

Series

MAX® 7000r

Datasheet

1.EPM7064STC44-10.pdf

(66 pages)

Specifications of EPM7256EGI192-20

Programmable Type

In System Programmable

Delay Time Tpd(1) Max

20.0ns

Voltage Supply - Internal

4.5 V ~ 5.5 V

Number Of Logic Elements/blocks

16

Number Of Macrocells

256

Number Of Gates

5000

Number Of I /o

164

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

192-PGA

Voltage

5V

Memory Type

EEPROM

Number Of Logic Elements/cells

16

Family Name

MAX 7000

# Macrocells

256

Number Of Usable Gates

5000

Frequency (max)

83.33MHz

Propagation Delay Time

20ns

Number Of Logic Blocks/elements

16

# I/os (max)

164

Operating Supply Voltage (typ)

5V

In System Programmable

Yes

Operating Supply Voltage (min)

4.5V

Operating Supply Voltage (max)

5.5V

Operating Temp Range

-40C to 85C

Operating Temperature Classification

Industrial

Mounting

Through Hole

Pin Count

192

Package Type

CPGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Features

-

Lead Free Status / Rohs Status

Compliant

Other names

544-2356

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

EPM7256EGI192-20

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

MAX 7000 Programmable Logic Device Family Data Sheet

52

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

Symbol

IN

IO

FIN

SEXP

PEXP

LAD

LAC

IOE

OD1

OD2

OD3

ZX1

ZX2

ZX3

XZ

SU

H

FSU

FH

RD

COMB

IC

EN

GLOB

PRE

CLR

PIA

LPA

Table 38. EPM7256S Internal Timing Parameters

Input pad and buffer delay

I/O input pad and buffer delay

Fast input delay

Shared expander delay

Parallel expander delay

Logic array delay

Logic control array delay

Internal output enable delay

Output buffer and pad delay

Output buffer and pad delay

Output buffer and pad delay

Output buffer enable delay

Output buffer enable delay

Output buffer enable delay

Output buffer disable delay

Register setup time

Register hold time

Register setup time of fast

input

Register hold time of fast

input

Register delay

Combinatorial delay

Array clock delay

Register enable time

Global control delay

Register preset time

Register clear time

PIA delay

Low-power adder

Parameter

C1 = 35 pF

C1 = 35 pF

C1 = 35 pF

C1 = 35 pF

C1 = 35 pF

C1 = 35 pF

C1 = 5 pF

(7)

(8)

Conditions

(6)

(6)

Note (1)

Min

1.1

1.6

2.4

0.6

-7

Max

10.0

2.9

0.3

0.3

3.4

3.9

1.1

2.6

2.6

0.8

0.5

1.0

5.5

4.0

4.5

9.0

4.0

1.1

1.1

2.6

2.8

2.7

2.7

3.0

Speed Grade

Min

2.0

3.0

3.0

0.5

-10

Max

11.0

0.5

0.5

1.0

5.0

0.8

5.0

5.0

2.0

1.5

2.0

5.5

5.0

5.5

9.0

5.0

2.0

2.0

5.0

5.0

1.0

3.0

3.0

1.0

Min

Altera Corporation

4.0

4.0

2.0

1.0

-15

Max

10.0

13.0

2.0

6.0

6.0

2.0

2.0

8.0

1.0

6.0

6.0

3.0

4.0

5.0

8.0

7.0

6.0

1.0

1.0

6.0

1.0

4.0

4.0

2.0

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns