CY3220LINBUS-RD Cypress Semiconductor Corp, CY3220LINBUS-RD Datasheet - Page 38

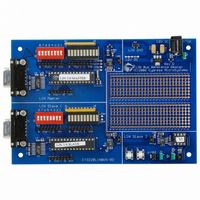

CY3220LINBUS-RD

Manufacturer Part Number

CY3220LINBUS-RD

Description

KIT REF DESIGN LIN BUS

Manufacturer

Cypress Semiconductor Corp

Series

PSoC®r

Datasheet

1.CY3220LINBUS-RD.pdf

(64 pages)

Specifications of CY3220LINBUS-RD

Main Purpose

Interface, LIN

Embedded

Yes, MCU, 8-Bit

Utilized Ic / Part

CY8C27143, CY8C27443

Processor To Be Evaluated

CY8C27143-24PXI and CY8C27443-24PXI

Interface Type

RS-232

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Contains lead / RoHS non-compliant

Other names

428-1926

4. Slave Design IP

regardless of which configuration is active, the GPIO state of

your main application is maintained. When you complete

this process, the TX and RX pins configuration looks like the

information in this table:

Table 4-1. TX Pin

Table 4-2. RX Pin

4.6.4

The next step is to route the signals to the digital blocks of

the LIN configurations.

1. Switch to Synchro Reception Configuration.

2. Route the RX Global_Input net to an appropriate

3. Select “Async” inside the Sync select square.

4. Select this Row_1_Input_x as the Capture input of the

5. Switch to Data Reception Configuration.

6. Route the RX Global_Input net to the same

7. Select “Async” inside the Sync select square.

8. Select this Row_1_Input_x as the input to the RX8 User

9. Route the output of the TX8 User Module through an

10. Switch to the base configuration

11. Make the connection between the Global_Input net and

12. 12. Make the connection between the Row_1_Output_x

With this routing of signals, the hardware configuration is

complete.

Note that in the LIN design for the CY8C21x34 family, the

same digital block used for RX8 is reconfigured into TX8 in

software during data transmission. So while using the

CY8C21x34 family, decide which Row Output net in which to

route the TX signal to a Global Out bus. Connect the output

of that Row Output net to the required Global Out bus in the

Data Reception Configuration and connect the Global Out

bus to the TX pin. Then, in the lin20slave.inc header file, set

36

Base

Synchro Reception TX

Data Reception

Base

Synchro Reception RX

Data Reception

Configuration

Configuration

Row_1_Input_x line.

Synchro_timer.

Row_1_Input_x net selected in the Synchro Reception

Configuration.

Module.

appropriate Row_1_Output_x line to the TX

Global_Output net.

the Row_1_Input_x net as done in the Data Reception

Configuration.

net and the Global_Output net in the Data Reception

Configuration.

Routing the Signals

TX

Name

TX

Name

RX

RX

As selected GlobalOut Strong

As selected StdCPU

As selected GlobalOut Strong

As selected GlobalIn High Z DisableInt

As selected GlobalIn High Z Change-

As selected GlobalIn High Z DisableInt

Port

Port

Select

Select

Drive

High Z

Drive

Cypress Semiconductor – Rev. **

FromRead

Interrupt

DisableInt

DisableInt

DisableInt

Interrupt

the appropriate ROW_OUTPUT_x equate to 1. While the

Data Reception Configuration is loaded, the RX8 block is

configured into a TX8 block and the primary output is con-

nected to the specified Row Output net.

4.6.5

You must configure the frames that belong to the slave. This

is done in the signaltable.asm file using the node capability

file or the LDF in which this node is described. For this

example, refer to the LDF provided in section 5,

Description File (LDF) on page

This example configures the slave CPM. As described in the

LDF file, this slave has three frames.

■

■

■

4.6.5.1

First, the buffers for these frames are allocated in RAM. A

name is given to each frame and the buffer is named as

Buffer<FrameName>. In our example, name the frames as

Frame1, Frame2 and Frame3. The buffers for these frames

are BufferFrame1, BufferFrame2, BufferFrame3. When allo-

cating RAM, one extra byte is allocated for each frame. This

byte is used as the status byte of that particular frame. The

LIN firmware updates the transaction status of each frame in

this byte. This byte also has the flag that indicates if a partic-

ular frame carries the Response_Error bit. This byte is the

first byte of the array. Apart from these buffers, there is

another buffer used by the LIN firmware for diagnostic

frames. This buffer is named as “abDiagBuffer.” Because

this buffer is only used during node configuration, it reuses

the same RAM location used by other frames. In the exam-

ple

BufferFrame1. If the application requires the frame signals

preserved during node configuration, then allocate nine

bytes for this buffer. If the total RAM for all the signals is less

than nine bytes, then also allocate nine bytes for the abDi-

agBuffer.

_abDiagBuffer:

_BufferFrame1:

_BufferFrame2:

_BufferFrame2:

abDiagBuffer:

BufferFrame1:

BufferFrame2:

BufferFrame2:

VL1_CEM_Frm1: This frame is published by the master

and is subscribed to by this slave. The message ID of

this frame is 0x1001. The length of this frame is eights

bytes.

VL1_CPM_Frm1: This frame is published by this slave

and is subscribed to by the master. The message ID of

this frame is 0x1002. The length of this frame is two

bytes.

VL1_CPM_Frm2: This frame is published by this slave

and is subscribed to by the master. The message ID of

this frame is 0x1003. The length of this frame is one

byte.

below,

Configuring the Signal Table

the

RAM Allocation

abDiagBuffer

blk 9

blk 3

blk 2

LIN Bus 2.0 Reference Design

43.

reuses

October 25, 2006

the

RAM

LIN

of