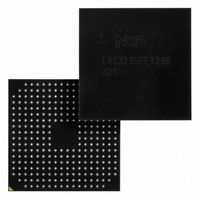

LPC3230FET296/01,5 NXP Semiconductors, LPC3230FET296/01,5 Datasheet - Page 22

LPC3230FET296/01,5

Manufacturer Part Number

LPC3230FET296/01,5

Description

IC ARM9 MCU 256K 296-TFBGA

Manufacturer

NXP Semiconductors

Series

LPC32x0r

Specifications of LPC3230FET296/01,5

Package / Case

296-TFBGA

Core Processor

ARM9

Core Size

16/32-Bit

Speed

266MHz

Connectivity

EBI/EMI, I²C, IrDA, Microwire, SPI, SSI, SSP, UART/USART, USB OTG

Peripherals

DMA, I²S, LCD, Motor Control PWM, PWM, WDT

Number Of I /o

51

Program Memory Type

ROMless

Ram Size

256K x 8

Voltage - Supply (vcc/vdd)

0.9 V ~ 3.6 V

Data Converters

A/D 3x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Processor Series

LPC32

Core

ARM926EJ-S

Data Bus Width

32 bit

Data Ram Size

256 KB

Interface Type

EMC

Maximum Clock Frequency

266 MHz

Number Of Timers

6

Operating Supply Voltage

1.31 V to 1.39 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 3 Channel

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

568-4964

935290764551

935290764551

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LPC3230FET296/01,5

Manufacturer:

NXP Semiconductors

Quantity:

10 000

NXP Semiconductors

LPC3220_30_40_50_1

Preliminary data sheet

7.1.3.2 Embedded trace buffer

7.2 AHB matrix

The Embedded Trace Module (ETM) is connected directly to the ARM core. It compresses

the trace information and exports it through a narrow trace port. An internal Embedded

Trace Buffer (ETB) of 2048

debugger control. Data from the ETB is recovered by the debug software through the

JTAG port.

The trace contains information about when the ARM core switches between states.

Instruction shows the flow of execution of the processor and provides a list of all the

instructions that were executed. Instruction trace is significantly compressed by only

broadcasting branch addresses as well as a set of status signals that indicate the pipeline

status on a cycle by cycle basis. For data accesses either data or address or both can be

traced.

The LPC3220/30/40/50 has a multi-layer AHB matrix for inter-block communication. AHB

is an ARM defined high-speed bus, which is part of the ARM bus architecture. AHB is a

high-bandwidth low-latency bus that supports multi-master arbitration and a bus

grant/request mechanism. For systems that have only one (CPU), or two (CPU and DMA)

bus masters a simple AHB works well. However, if a system requires multiple bus masters

and the CPU needs access to external memory, a single AHB bus can cause a bottleneck.

To increase performance, the LPC3220/30/40/50 uses an expanded AHB architecture

known as Multi-layer AHB. A Multi-layer AHB replaces the request/grant and arbitration

mechanism used in a simple AHB with an interconnect matrix that moves arbitration out

toward the slave devices. Thus, if a CPU and a DMA controller want access to the same

memory, the interconnect matrix arbitrates between the two when granting access to the

memory. This advanced architecture allows simultaneous access by bus masters to

different resources with an increase in arbitration complexity. In this architectural

implementation, removing guaranteed central arbitration and allowing more than one bus

master to be active at the same time provides better overall microcontroller performance.

In the LPC3220/30/40/50, the multi-Layer AHB system has a separate bus for each of

seven AHB Masters:

There are no arbitration delays unless two masters attempt to access the same slave at

the same time.

•

•

•

•

•

•

•

CPU data bus

CPU instruction bus

General purpose DMA Master 0

General purpose DMA Master 1

Ethernet controller

USB controller

LCD controller

Rev. 01 — 6 February 2009

24 bits captures the trace information under software

LPC3220/30/40/50

16/32-bit ARM microcontrollers

© NXP B.V. 2009. All rights reserved.

22 of 73