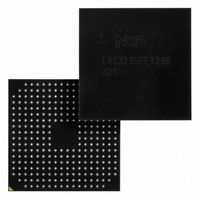

LPC3230FET296/01,5 NXP Semiconductors, LPC3230FET296/01,5 Datasheet - Page 29

LPC3230FET296/01,5

Manufacturer Part Number

LPC3230FET296/01,5

Description

IC ARM9 MCU 256K 296-TFBGA

Manufacturer

NXP Semiconductors

Series

LPC32x0r

Specifications of LPC3230FET296/01,5

Package / Case

296-TFBGA

Core Processor

ARM9

Core Size

16/32-Bit

Speed

266MHz

Connectivity

EBI/EMI, I²C, IrDA, Microwire, SPI, SSI, SSP, UART/USART, USB OTG

Peripherals

DMA, I²S, LCD, Motor Control PWM, PWM, WDT

Number Of I /o

51

Program Memory Type

ROMless

Ram Size

256K x 8

Voltage - Supply (vcc/vdd)

0.9 V ~ 3.6 V

Data Converters

A/D 3x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Processor Series

LPC32

Core

ARM926EJ-S

Data Bus Width

32 bit

Data Ram Size

256 KB

Interface Type

EMC

Maximum Clock Frequency

266 MHz

Number Of Timers

6

Operating Supply Voltage

1.31 V to 1.39 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 3 Channel

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

568-4964

935290764551

935290764551

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LPC3230FET296/01,5

Manufacturer:

NXP Semiconductors

Quantity:

10 000

NXP Semiconductors

LPC3220_30_40_50_1

Preliminary data sheet

7.6.3.2 USB host controller

7.6.3.3 USB OTG controller

condition is indicated via status registers. An interrupt is also generated if enabled. The

DMA controller when enabled transfers data between the endpoint buffer and the USB

RAM.

Features

The host controller enables data exchange with various USB devices attached to the bus.

It consists of register interface, serial interface engine and DMA controller. The register

interface complies to the OHCI specification .

Features

USB OTG (On-The-Go) is a supplement to the USB 2.0 specification that augments the

capability of existing mobile devices and USB peripherals by adding host functionality for

connection to USB peripherals.

Features

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

Fully compliant with USB 2.0 full-speed specification .

Supports 32 physical (16 logical) endpoints.

Supports control, bulk, interrupt and isochronous endpoints.

Scalable realization of endpoints at run time.

Endpoint maximum packet size selection (up to USB maximum specification) by

software at run time.

RAM message buffer size based on endpoint realization and maximum packet size.

Supports bus-powered capability with low suspend current.

Supports DMA transfer on all non-control endpoints.

One duplex DMA channel serves all endpoints.

Allows dynamic switching between CPU controlled and DMA modes.

Double buffer implementation for bulk and isochronous endpoints.

OHCI compliant.

OHCI specifies the operation and interface of the USB host controller and software

driver.

The host controller has four USB states visible to the software driver:

– USBOperational: Process lists and generate SOF tokens.

– USBReset: Forces reset signaling on the bus, SOF disabled.

– USBSuspend: Monitor USB for wake-up activity.

– USBResume: Forces resume signaling on the bus.

HCCA register points to interrupt and isochronous descriptors list.

ControlHeadED and BulkHeadED registers point to control and bulk descriptors list.

Fully compliant with On-The-Go supplement to the USB Specification 2.0 Revision

1.0 .

Rev. 01 — 6 February 2009

LPC3220/30/40/50

16/32-bit ARM microcontrollers

© NXP B.V. 2009. All rights reserved.

29 of 73