AT91SAM7S32-AU-001 Atmel, AT91SAM7S32-AU-001 Datasheet - Page 484

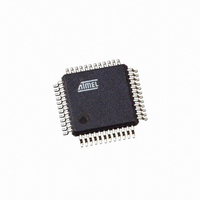

AT91SAM7S32-AU-001

Manufacturer Part Number

AT91SAM7S32-AU-001

Description

IC ARM7 MCU 32BIT 32K 48LQFP

Manufacturer

Atmel

Series

AT91SAMr

Specifications of AT91SAM7S32-AU-001

Core Processor

ARM7

Core Size

16/32-Bit

Speed

55MHz

Connectivity

I²C, SPI, SSC, UART/USART

Peripherals

Brown-out Detect/Reset, POR, PWM, WDT

Number Of I /o

21

Program Memory Size

32KB (32K x 8)

Program Memory Type

FLASH

Ram Size

8K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 1.95 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

48-LQFP

For Use With

AT91SAM7S-EK - KIT EVAL FOR ARM AT91SAM7S

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Other names

AT91SAM7S32-AU001

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 484 of 779

- Download datasheet (11Mb)

34.5.3

34.5.3.1

34.5.3.2

34.5.3.3

484

AT91SAM7S Series Preliminary

PWM Controller Operations

Initialization

Source Clock Selection Criteria

Changing the Duty Cycle or the Period

Before enabling the output channel, this channel must have been configured by the software

application:

It is possible to synchronize different channels by enabling them at the same time by means of

writing simultaneously several CHIDx bits in the PWM_ENA register.

The large number of source clocks can make selection difficult. The relationship between the

value in the Period Register (PWM_CPRDx) and the Duty Cycle Register (PWM_CDTYx) can

help the user in choosing. The event number written in the Period Register gives the PWM accu-

racy. The Duty Cycle quantum cannot be lower than 1/PWM_CPRDx value. The higher the value

of PWM_CPRDx, the greater the PWM accuracy.

For example, if the user sets 15 (in decimal) in PWM_CPRDx, the user is able to set a value

between 1 up to 14 in PWM_CDTYx Register. The resulting duty cycle quantum cannot be lower

than 1/15 of the PWM period.

It is possible to modulate the output waveform duty cycle or period.

To prevent unexpected output waveform, the user must use the update register (PWM_CUPDx)

to change waveform parameters while the channel is still enabled. The user can write a new

period value or duty cycle value in the update register (PWM_CUPDx). This register holds the

new value until the end of the current cycle and updates the value for the next cycle. Depending

on the CPD field in the PWM_CMRx register, PWM_CUPDx either updates PWM_CPRDx or

PWM_CDTYx. Note that even if the update register is used, the period must not be smaller than

the duty cycle.

• Configuration of the clock generator if DIVA and DIVB are required

• Selection of the clock for each channel (CPRE field in the PWM_CMRx register)

• Configuration of the waveform alignment for each channel (CALG field in the PWM_CMRx

• Configuration of the period for each channel (CPRD in the PWM_CPRDx register). Writing in

• Configuration of the duty cycle for each channel (CDTY in the PWM_CDTYx register).

• Configuration of the output waveform polarity for each channel (CPOL in the PWM_CMRx

• Enable Interrupts (Writing CHIDx in the PWM_IER register)

• Enable the PWM channel (Writing CHIDx in the PWM_ENA register)

• In such a situation, all channels may have the same clock selector configuration and the

register)

PWM_CPRDx Register is possible while the channel is disabled. After validation of the

channel, the user must use PWM_CUPDx Register to update PWM_CPRDx as explained

below.

Writing in PWM_CDTYx Register is possible while the channel is disabled. After validation of

the channel, the user must use PWM_CUPDx Register to update PWM_CDTYx as explained

below.

register)

same period specified.

6175K–ATARM–30-Aug-10

Related parts for AT91SAM7S32-AU-001

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AT91 ARM Thumb-based Microcontrollers

Manufacturer:

ATMEL [ATMEL Corporation]

Datasheet:

Part Number:

Description:

IC ARM7 MCU FLASH 32K 48QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU ARM7 32KB FLASH 48LQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU ARM7 32KB FLASH 48-VQFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet: