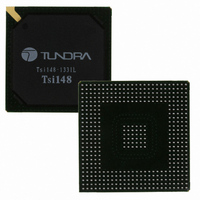

TSI148-133IL IDT, Integrated Device Technology Inc, TSI148-133IL Datasheet - Page 72

TSI148-133IL

Manufacturer Part Number

TSI148-133IL

Description

IC PCI-VME BRIDGE 456PBGA

Manufacturer

IDT, Integrated Device Technology Inc

Series

Tsi148&Trade;r

Datasheets

1.TSI148-133CL.pdf

(391 pages)

2.TSI148-133CL.pdf

(2 pages)

3.TSI148-133CL.pdf

(12 pages)

Specifications of TSI148-133IL

Applications

PCI-to-VME Bridge

Interface

PCI

Voltage - Supply

3.3V

Package / Case

456-PBGA

Mounting Type

Surface Mount

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Other names

800-1905

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

TSI148-133IL

Manufacturer:

IDT

Quantity:

47

Company:

Part Number:

TSI148-133IL

Manufacturer:

IDT, Integrated Device Technology Inc

Quantity:

10 000

Company:

Part Number:

TSI148-133ILY

Manufacturer:

SUMPLUS

Quantity:

210

Company:

Part Number:

TSI148-133ILY

Manufacturer:

IDT

Quantity:

201

- Current page: 72 of 391

- Download datasheet (2Mb)

3. PCI/X Interface > PCI Mode

72

When a PCI bus memory read line burst transfer is received, the read command passed to the

Linkage Module requests 32 bytes. When a PCI bus memory read multiple command is

received, the data size depends on the PFS bits. The read sizes are 64, 128, 256, or 512 bytes.

The PCI read operations are summarized in

Table 3: PCI Read Data Size

The PCI bus master is retried until all the requested data is available in the PCI Target read

buffer. The read then completes on the PCI bus.

Single Beat

Transfer

Burst

Burst

Burst

Burst

Burst

Burst

Burst

PCI

Care must be used when setting the value in the PFS field because the VMEbus

read is completed before data is transferred on the PCI bus. If the value is too

large, time is wasted reading data that is not used. If the value is too small,

additional PCI bus commands are required. The optimum setting depends on the

PCI bus masters and the requirements of the application. In many cases, the only

read transfers from the PCI bus to the VMEbus are single beat processor load

operations and prefetching is not required.

Read Multiple

Read Multiple

Read Multiple

Read Multiple

Command

Read Line

Read

Read

PCI

X

MRPFD

Table

Bit

X

X

X

X

X

X

1

0

3.

Tsi148 PCI/X-to-VME Bus Bridge User Manual

PFS

Bits

X

X

X

X

0

1

2

3

80A3020_MA001_13

Single Beat

Single Beat

Command

128 bytes

256 bytes

512 bytes

Linkage

32 bytes

32 bytes

64 bytes

Related parts for TSI148-133IL

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC PCI-VME BRIDGE 456PBGA

Manufacturer:

IDT, Integrated Device Technology Inc

Datasheet:

Part Number:

Description:

TRANSLATION DEVICE DPI 80-PQFP

Manufacturer:

IDT, Integrated Device Technology Inc

Datasheet:

Part Number:

Description:

IDT PART

Manufacturer:

IDT, Integrated Device Technology Inc

Datasheet:

Part Number:

Description:

IC LIU T1/E1/J1 OCTAL 256PBGA

Manufacturer:

IDT, Integrated Device Technology Inc

Datasheet:

Part Number:

Description:

IC FREQ TIMING GENERATOR 28TSSOP

Manufacturer:

IDT, Integrated Device Technology Inc

Datasheet:

Part Number:

Description:

IC CLK DVR PLL 1:10 40VFQFPN

Manufacturer:

IDT, Integrated Device Technology Inc

Datasheet:

Part Number:

Description:

IC CLK FANOUT BUFFER 1:18 32LQFP

Manufacturer:

IDT, Integrated Device Technology Inc

Datasheet:

Part Number:

Description:

IC CLK FANOUT BUFFER 1:18 32LQFP

Manufacturer:

IDT, Integrated Device Technology Inc

Datasheet:

Part Number:

Description:

IC CK505 VREG/RES 56TSSOP

Manufacturer:

IDT, Integrated Device Technology Inc

Datasheet:

Part Number:

Description:

IC SDRAM CLK DVR 1:10 48-TSSOP

Manufacturer:

IDT, Integrated Device Technology Inc

Datasheet:

Part Number:

Description:

IC CLK DVR PLL 1:10 48TSSOP

Manufacturer:

IDT, Integrated Device Technology Inc

Datasheet:

Part Number:

Description:

IC FLEXPC CLK PROGR P4 56-TSSOP

Manufacturer:

IDT, Integrated Device Technology Inc

Datasheet:

Part Number:

Description:

IC FLEXPC CLK PROGR P4 56-TSSOP

Manufacturer:

IDT, Integrated Device Technology Inc

Datasheet:

Part Number:

Description:

IC FLEXPC CLK PROGR P4 56-SSOP

Manufacturer:

IDT, Integrated Device Technology Inc

Datasheet:

Part Number:

Description:

IC PLL CLK DRIVER 2.5V 28-TSSOP

Manufacturer:

IDT, Integrated Device Technology Inc

Datasheet: