STEVAL-PSQ001V1 STMicroelectronics, STEVAL-PSQ001V1 Datasheet - Page 42

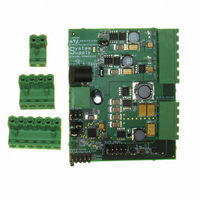

STEVAL-PSQ001V1

Manufacturer Part Number

STEVAL-PSQ001V1

Description

BOARD EVAL BASED ON PM6680A

Manufacturer

STMicroelectronics

Type

Other Power Managementr

Specifications of STEVAL-PSQ001V1

Design Resources

STEVAL-PSQ001V1 Gerber Files STEVAL-PSQ001V1 Schematic STEVAL-PSQ001V1 Bill of Material

Main Purpose

DC/DC, Step Down with LDO

Outputs And Type

6, Non-Isolated

Voltage - Output

0.9 ~ 2.5 V, 1 ~ 3.3 V, 2x 3.3 V, 2.5 V, 5 V

Current - Output

4A, 2A, 800mA, 400mA, 400mA, 150mA

Voltage - Input

5 ~ 36V

Regulator Topology

Buck

Frequency - Switching

200kHz, 300kHz

Board Type

Fully Populated

Utilized Ic / Part

PM6680A

Input Voltage

5 V to 36 V

Output Voltage

1 V to 3.3 V

Product

Power Management Modules

Silicon Manufacturer

ST Micro

Silicon Core Number

PM6680A

Kit Application Type

Power Management

Application Sub Type

Power Supply

Kit Contents

Board

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Power - Output

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

For Use With/related Products

PM6680A

Other names

497-6425

STEVAL-PSQ001V1

STEVAL-PSQ001V1

Design guidelines

42/48

Equation 41

5.

6.

7.

8.

9.

●

●

●

●

(Let's assume Tmax=75 °C in R

R

Input capacitor

Maximum input capacitor RMS current is about 1.084 A. Then I

We put two 10 µF ceramic capacitors with Irms = 1.5 A.

Synchronous rectifier

OUT1: Shottky diode STPS1L40M

OUT2: Shottky diode STPS1L40M

Integrator loop

(Refer to figure 14)

OUT1: The ripple is smaller than 40 mV, then the virtual ESR network is required.

C

OUT2: The ripple is smaller than 40 mV, then the virtual ESR network is required.

C

Output feedback divider

(Refer to figure 6)

OUT1: R1 = 10 kΩ; R2 = 27 kΩ

OUT2: R1 = 10 kΩ; R2 = 10 kΩ

Layout guidelines

The layout is very important in terms of efficiency, stability and noise of the system. It is

possible to refer to the PM6680A demoboard for a complete layout example.

For good PC board layout follows these guidelines:

Place on the top side all the power components (inductors, input and output capacitors,

MOSFETs and diodes). Refer them to a power ground plan, PGND. If possible, reserve

a layer to PGND plan. The PGND plan is the same for both the switching sections.

AC current paths layout is very critical (see

their length. Trace the LS MOSFET connection to PGND plan as short as possible.

Place the synchronous diode D near the LS MOSFET. Connect the LS MOSFET drain

to the switching node with a short trace.

Place input capacitors near HS MOSFET drain. It is recommended to use the same

input voltage plan for both the switching sections, in order to put together all input

capacitors.

Place all the sensitive analog signals (feedbacks, voltage reference, current sense

paths) on the bottom side of the board or in an inner layer. Isolate them from the power

top side with a signal ground layer, SGND. Connect the SGND and PGND plans only in

one point (a multiple vias connection is preferable to a 0 ohm resistor connection) near

the PGND device pin. Place the device on the top or on the bottom size and connect

the exposed pad and the SGND pins to the SGND plan (see

CSENSE

INT

INT

= 1.5 nF; C

=1.5 nF; C

= 560 Ω.

filt

filt

=47 pF; R

= 47 pF; R

INT

INT

= 820 Ω

DSon

= 1.1 kΩ

calculation). We choose standard value

Figure 41

). The first priority is to minimize

Figure 41

CINRMS

).

> 1.084 A

PM6680A