PIC16F690DM-PCTLHS Microchip Technology, PIC16F690DM-PCTLHS Datasheet - Page 189

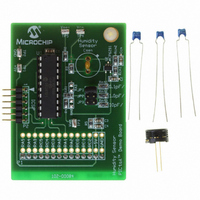

PIC16F690DM-PCTLHS

Manufacturer Part Number

PIC16F690DM-PCTLHS

Description

BOARD DEMO PICTAIL HUMIDITY SNSR

Manufacturer

Microchip Technology

Series

PICtail™r

Datasheets

1.PIC16F690DM-PCTLHS.pdf

(36 pages)

2.PIC16F690DM-PCTLHS.pdf

(32 pages)

3.PIC16F690DM-PCTLHS.pdf

(306 pages)

4.PIC16F690DM-PCTLHS.pdf

(14 pages)

Specifications of PIC16F690DM-PCTLHS

Sensor Type

Humidity

Sensing Range

1 ~ 99% RH

Interface

Analog

Voltage - Supply

5V

Embedded

Yes, MCU, 8-Bit

Utilized Ic / Part

MCP6291, PIC16F690

Processor To Be Evaluated

MCP6291 and PIC16F690

Interface Type

ICSP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

AC162061 - HEADER INTRFC MPLAB ICD2 20PIN

Sensitivity

-

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

- PIC16F690DM-PCTLHS PDF datasheet

- PIC16F690DM-PCTLHS PDF datasheet #2

- PIC16F690DM-PCTLHS PDF datasheet #3

- PIC16F690DM-PCTLHS PDF datasheet #4

- Current page: 189 of 306

- Download datasheet (6Mb)

13.8

In Master mode, all module clocks are halted and the

transmission/reception will remain in that state until the

device wakes from Sleep. After the device returns to

Normal mode, the module will continue to transmit/

receive data.

In Slave mode, the SPI Transmit/Receive Shift register

operates asynchronously to the device. This allows the

device to be placed in Sleep mode and data to be

shifted into the SPI Transmit/Receive Shift register.

When all 8 bits have been received, the SSP interrupt

flag bit will be set and if enabled, will wake the device

from Sleep.

13.9

A Reset disables the SSP module and terminates the

current transfer.

TABLE 13-2:

© 2008 Microchip Technology Inc.

0Bh/8Bh/

10Bh/18Bh

0Ch

13h

14h

86h/186h

87h/187h

8Ch

94h

Legend:

Address

Note 1:

Sleep Operation

Effects of a Reset

x = unknown, u = unchanged, – = unimplemented, read as ‘0’. Shaded cells are not used by the SSP in SPI mode.

INTCON

PIR1

SSPBUF

SSPCON

TRISB

TRISC

PIE1

SSPSTAT

PIC16F677/PIC16F687/PIC16F689/PIC16F690 only.

Name

REGISTERS ASSOCIATED WITH SPI OPERATION

Synchronous Serial Port Receive Buffer/Transmit Register

TRISB7

TRISC7

WCOL

Bit 7

SMP

GIE

—

—

TRISC6

SSPOV

TRISB6

Bit 6

PEIE

ADIF

ADIE

CKE

PIC16F631/677/685/687/689/690

TRISB5

TRISC5

SSPEN

Bit 5

RCIF

RCIE

T0IE

D/A

TRISC4

TRISB4

Bit 4

INTE

TXIE

TXIF

CKP

P

TRISC3

SSPM3

RABIE

SSPIE

SSPIF

Bit 3

—

S

13.10 Bus Mode Compatibility

Table 13-1 shows the compatibility between the

standard SPI modes and the states of the CKP and

CKE control bits.

TABLE 13-1:

There is also a SMP bit which controls when the data is

sampled.

Standard SPI Mode

CCP1IF

TRISC2

CCP1IE

Terminology

SSPM2

Bit 2

T0IF

R/W

—

0, 0

0, 1

1, 0

1, 1

(1)

TMR2IE

TMR2IF

TRISC1

SSPM1

Bit 1

INTF

UA

—

SPI BUS MODES

TMR1IF

TRISC0

TMR1IE

SSPM0

RABIF

Bit 0

BF

—

CKP

Control Bits State

0

0

1

1

0000 000x

-000 0000

xxxx xxxx

0000 0000

1111 ----

1111 1111

-000 0000

0000 0000

Value on

POR,

BOR

DS41262E-page 187

0000 000x

-000 0000

uuuu uuuu

0000 0000

1111 ----

1111 1111

-000 0000

0000 0000

CKE

Value on

all other

Resets

1

0

1

0

Related parts for PIC16F690DM-PCTLHS

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet: