PIC16F690DM-PCTLHS Microchip Technology, PIC16F690DM-PCTLHS Datasheet - Page 41

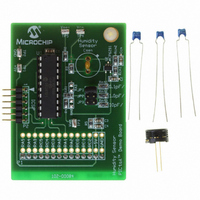

PIC16F690DM-PCTLHS

Manufacturer Part Number

PIC16F690DM-PCTLHS

Description

BOARD DEMO PICTAIL HUMIDITY SNSR

Manufacturer

Microchip Technology

Series

PICtail™r

Datasheets

1.PIC16F690DM-PCTLHS.pdf

(36 pages)

2.PIC16F690DM-PCTLHS.pdf

(32 pages)

3.PIC16F690DM-PCTLHS.pdf

(306 pages)

4.PIC16F690DM-PCTLHS.pdf

(14 pages)

Specifications of PIC16F690DM-PCTLHS

Sensor Type

Humidity

Sensing Range

1 ~ 99% RH

Interface

Analog

Voltage - Supply

5V

Embedded

Yes, MCU, 8-Bit

Utilized Ic / Part

MCP6291, PIC16F690

Processor To Be Evaluated

MCP6291 and PIC16F690

Interface Type

ICSP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

AC162061 - HEADER INTRFC MPLAB ICD2 20PIN

Sensitivity

-

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

- PIC16F690DM-PCTLHS PDF datasheet

- PIC16F690DM-PCTLHS PDF datasheet #2

- PIC16F690DM-PCTLHS PDF datasheet #3

- PIC16F690DM-PCTLHS PDF datasheet #4

- Current page: 41 of 306

- Download datasheet (6Mb)

2.2.2.4

The PIE1 register contains the interrupt enable bits, as

shown in Register 2-4.

REGISTER 2-4:

© 2008 Microchip Technology Inc.

bit 7

Legend:

R = Readable bit

-n = Value at POR

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

Note 1:

U-0

—

2:

3:

4:

5:

PIC16F685/PIC16F690 only.

PIC16F685/PIC16F689/PIC16F690 only.

PIC16F687/PIC16F689/PIC16F690 only.

PIC16F677/PIC16F687/PIC16F689/PIC16F690 only.

PIC16F677/PIC16F685/PIC16F687/PIC16F689/PIC16F690 only.

PIE1 Register

Unimplemented: Read as ‘0’

ADIE: A/D Converter (ADC) Interrupt Enable bit

1 = Enables the ADC interrupt

0 = Disables the ADC interrupt

RCIE: EUSART Receive Interrupt Enable bit

1 = Enables the EUSART receive interrupt

0 = Disables the EUSART receive interrupt

TXIE: EUSART Transmit Interrupt Enable bit

1 = Enables the EUSART transmit interrupt

0 = Disables the EUSART transmit interrupt

SSPIE: Synchronous Serial Port (SSP) Interrupt Enable bit

1 = Enables the SSP interrupt

0 = Disables the SSP interrupt

CCP1IE: CCP1 Interrupt Enable bit

1 = Enables the CCP1 interrupt

0 = Disables the CCP1 interrupt

TMR2IE: Timer2 to PR2 Match Interrupt Enable bit

1 = Enables the Timer2 to PR2 match interrupt

0 = Disables the Timer2 to PR2 match interrupt

TMR1IE: Timer1 Overflow Interrupt Enable bit

1 = Enables the Timer1 overflow interrupt

0 = Disables the Timer1 overflow interrupt

ADIE

R/W-0

PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

(5)

W = Writable bit

‘1’ = Bit is set

RCIE

R/W-0

PIC16F631/677/685/687/689/690

(3)

TXIE

R/W-0

(2)

(3)

U = Unimplemented bit, read as ‘0’

‘0’ = Bit is cleared

(3)

(5)

SSPIE

R/W-0

(5)

Note:

(1)

(4)

Bit PEIE of the INTCON register must be

set to enable any peripheral interrupt.

(4)

CCP1IE

R/W-0

(2)

x = Bit is unknown

TMR2IE

R/W-0

(1)

DS41262E-page 39

TMR1IE

R/W-0

bit 0

Related parts for PIC16F690DM-PCTLHS

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet: