PIC16F690DM-PCTLHS Microchip Technology, PIC16F690DM-PCTLHS Datasheet - Page 205

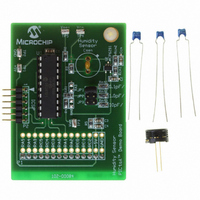

PIC16F690DM-PCTLHS

Manufacturer Part Number

PIC16F690DM-PCTLHS

Description

BOARD DEMO PICTAIL HUMIDITY SNSR

Manufacturer

Microchip Technology

Series

PICtail™r

Datasheets

1.PIC16F690DM-PCTLHS.pdf

(36 pages)

2.PIC16F690DM-PCTLHS.pdf

(32 pages)

3.PIC16F690DM-PCTLHS.pdf

(306 pages)

4.PIC16F690DM-PCTLHS.pdf

(14 pages)

Specifications of PIC16F690DM-PCTLHS

Sensor Type

Humidity

Sensing Range

1 ~ 99% RH

Interface

Analog

Voltage - Supply

5V

Embedded

Yes, MCU, 8-Bit

Utilized Ic / Part

MCP6291, PIC16F690

Processor To Be Evaluated

MCP6291 and PIC16F690

Interface Type

ICSP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

AC162061 - HEADER INTRFC MPLAB ICD2 20PIN

Sensitivity

-

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

- PIC16F690DM-PCTLHS PDF datasheet

- PIC16F690DM-PCTLHS PDF datasheet #2

- PIC16F690DM-PCTLHS PDF datasheet #3

- PIC16F690DM-PCTLHS PDF datasheet #4

- Current page: 205 of 306

- Download datasheet (6Mb)

14.2.5

On power-up, the time-out sequence is as follows: first,

PWRT time-out is invoked after POR has expired, then

OST is activated after the PWRT time-out has expired.

The total time-out will vary based on oscillator

configuration and PWRTE bit status. For example, in

EC mode with PWRTE bit erased (PWRT disabled),

there will be no time-out at all. Figures 14-4, 14-5

and 14-6 depict time-out sequences. The device can

execute code from the INTOSC while OST is active by

enabling Two-Speed Start-up or Fail-Safe Monitor (see

Section 3.7.2 “Two-speed Start-up Sequence” and

Section 3.8 “Fail-Safe Clock Monitor”).

Since the time-outs occur from the POR pulse, if MCLR

is kept low long enough, the time-outs will expire. Then,

bringing MCLR high will begin execution immediately

(see Figure 14-5). This is useful for testing purposes or

to synchronize more than one PIC16F631/677/685/

687/689/690 device operating in parallel.

Table 14-5 shows the Reset conditions for some

special registers, while Table 14-4 shows the Reset

conditions for all the registers.

TABLE 14-1:

TABLE 14-2:

TABLE 14-3:

© 2008 Microchip Technology Inc.

XT, HS, LP

LP, T1OSCIN = 1

RC, EC, INTOSC

PCON

STATUS

Legend:

Note

Legend: u = unchanged, x = unknown

Oscillator Configuration

POR

Name

0

u

u

u

u

u

1:

u = unchanged, x = unknown, – = unimplemented bit, reads as ‘0’, q = value depends on condition. Shaded cells are not used by BOR.

Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

TIME-OUT SEQUENCE

BOR

Bit 7

x

0

u

u

u

u

IRP

—

TIME-OUT IN VARIOUS SITUATIONS

STATUS/PCON BITS AND THEIR SIGNIFICANCE

SUMMARY OF REGISTERS ASSOCIATED WITH BROWN-OUT

Bit 6

RP1

TO

—

1

1

0

0

u

1

PWRTE = 0

1024 • T

ULPWUE

T

T

T

PWRT

Bit 5

RPO

PWRT

PWRT

PIC16F631/677/685/687/689/690

PD

1

1

u

0

u

0

OSC

+

Power-up

SBOREN

Bit 4

Power-on Reset

Brown-out Reset

WDT Reset

WDT Wake-up

MCLR Reset during normal operation

MCLR Reset during Sleep

TO

PWRTE = 1

1024 • T

Bit 3

—

—

PD

—

OSC

14.2.6

The Power Control register PCON (address 8Eh) has

two Status bits to indicate what type of Reset that last

occurred.

Bit 0 is BOR (Brown-out Reset). BOR is unknown on

Power-on Reset. It must then be set by the user and

checked on subsequent Resets to see if BOR = 0,

indicating that a Brown-out has occurred. The BOR

Status bit is a “don’t care” and is not necessarily

predictable if the brown-out circuit is disabled

(BOREN<1:0>

register).

Bit 1 is POR (Power-on Reset). It is a ‘0’ on Power-on

Reset and unaffected otherwise. The user must write a

‘1’ to this bit following a Power-on Reset. On a

subsequent Reset, if POR is ‘0’, it will indicate that a

Power-on Reset has occurred (i.e., V

gone too low).

For more information, see Section 4.2.4 “Ultra Low-

Power Wake-up” and Section 14.2.4 “Brown-out

Reset (BOR)”.

Bit 2

—

Z

PWRTE = 0

1024 • T

T

T

T

PWRT

PWRT

PWRT

Brown-out Reset

Bit 1

POR

DC

POWER CONTROL (PCON)

REGISTER

Condition

OSC

+

= 00 in the Configuration Word

Bit 0

BOR

C

1024 • T

PWRTE = 1

—

—

--01 --qq

0001 1xxx

POR, BOR

OSC

Value on

DS41262E-page 203

Wake-up from

1024 • T

DD

Sleep

--0u --uu

000q quuu

may have

Value on

—

—

all other

Resets

OSC

Related parts for PIC16F690DM-PCTLHS

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet: