PIC16F690DM-PCTLHS Microchip Technology, PIC16F690DM-PCTLHS Datasheet - Page 43

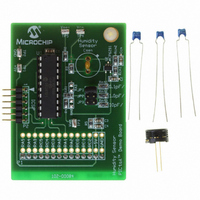

PIC16F690DM-PCTLHS

Manufacturer Part Number

PIC16F690DM-PCTLHS

Description

BOARD DEMO PICTAIL HUMIDITY SNSR

Manufacturer

Microchip Technology

Series

PICtail™r

Datasheets

1.PIC16F690DM-PCTLHS.pdf

(36 pages)

2.PIC16F690DM-PCTLHS.pdf

(32 pages)

3.PIC16F690DM-PCTLHS.pdf

(306 pages)

4.PIC16F690DM-PCTLHS.pdf

(14 pages)

Specifications of PIC16F690DM-PCTLHS

Sensor Type

Humidity

Sensing Range

1 ~ 99% RH

Interface

Analog

Voltage - Supply

5V

Embedded

Yes, MCU, 8-Bit

Utilized Ic / Part

MCP6291, PIC16F690

Processor To Be Evaluated

MCP6291 and PIC16F690

Interface Type

ICSP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

AC162061 - HEADER INTRFC MPLAB ICD2 20PIN

Sensitivity

-

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

- PIC16F690DM-PCTLHS PDF datasheet

- PIC16F690DM-PCTLHS PDF datasheet #2

- PIC16F690DM-PCTLHS PDF datasheet #3

- PIC16F690DM-PCTLHS PDF datasheet #4

- Current page: 43 of 306

- Download datasheet (6Mb)

2.2.2.6

The PIR1 register contains the interrupt flag bits, as

shown in Register 2-6.

REGISTER 2-6:

© 2008 Microchip Technology Inc.

bit 7

Legend:

R = Readable bit

-n = Value at POR

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

Note 1:

U-0

—

2:

3:

4:

5:

PIC16F685/PIC16F690 only.

PIC16F685/PIC16F689/PIC16F690 only.

PIC16F687/PIC16F689/PIC16F690 only.

PIC16F677/PIC16F687/PIC16F689/PIC16F690 only.

PIC16F677/PIC16F685/PIC16F687/PIC16F689/PIC16F690 only.

PIR1 Register

Unimplemented: Read as ‘0’

ADIF: A/D Converter Interrupt Flag bit

1 = A/D conversion complete (must be cleared in software)

0 = A/D conversion has not completed or has not been started

RCIF: EUSART Receive Interrupt Flag bit

1 = The EUSART receive buffer is full (cleared by reading RCREG)

0 = The EUSART receive buffer is not full

TXIF: EUSART Transmit Interrupt Flag bit

1 = The EUSART transmit buffer is empty (cleared by writing to TXREG)

0 = The EUSART transmit buffer is full

SSPIF: Synchronous Serial Port (SSP) Interrupt Flag bit

1 = The Transmission/Reception is complete (must be cleared in software)

0 = Waiting to Transmit/Receive

CCP1IF: CCP1 Interrupt Flag bit

Capture mode:

Compare mode:

PWM mode:

Unused in this mode

TMR2IF: Timer2 to PR2 Interrupt Flag bit

1 = A Timer2 to PR2 match occurred (must be cleared in software)

0 = No Timer2 to PR2 match occurred

TMR1IF: Timer1 Overflow Interrupt Flag bit

1 = The TMR1 register overflowed (must be cleared in software)

0 = The TMR1 register did not overflow

ADIF

R/W-0

1 = A TMR1 register capture occurred (must be cleared in software)

0 = No TMR1 register capture occurred

1 = A TMR1 register compare match occurred (must be cleared in software)

0 = No TMR1 register compare match occurred

PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

(5)

W = Writable bit

‘1’ = Bit is set

RCIF

PIC16F631/677/685/687/689/690

R-0

(3)

TXIF

(2)

R-0

(3)

(5)

(1)

(3)

(3)

U = Unimplemented bit, read as ‘0’

‘0’ = Bit is cleared

SSPIF

R/W-0

Note:

(4)

(4)

Interrupt flag bits are set when an interrupt

condition occurs, regardless of the state of

its corresponding enable bit or the global

enable bit, GIE of the INTCON register.

User

appropriate interrupt flag bits are clear

prior to enabling an interrupt.

CCP1IF

R/W-0

software

(2)

x = Bit is unknown

TMR2IF

R/W-0

should

(1)

DS41262E-page 41

ensure

TMR1IF

R/W-0

bit 0

the

Related parts for PIC16F690DM-PCTLHS

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet: