M30260F6AGP#U5A Renesas Electronics America, M30260F6AGP#U5A Datasheet - Page 232

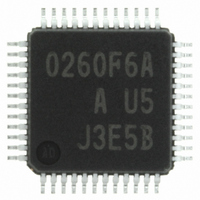

M30260F6AGP#U5A

Manufacturer Part Number

M30260F6AGP#U5A

Description

IC M16C MCU FLASH 48K 48LQFP

Manufacturer

Renesas Electronics America

Series

M16C™ M16C/Tiny/26r

Datasheet

1.M30260F3AGPU5A.pdf

(354 pages)

Specifications of M30260F6AGP#U5A

Core Processor

M16C/60

Core Size

16-Bit

Speed

20MHz

Connectivity

I²C, IEBus, SIO, UART/USART

Peripherals

DMA, PWM, Voltage Detect, WDT

Number Of I /o

39

Program Memory Size

48KB (48K x 8)

Program Memory Type

FLASH

Ram Size

2K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 12x10b

Oscillator Type

Internal

Operating Temperature

-20°C ~ 85°C

Package / Case

48-LQFP

Cpu Family

R8C

Device Core Size

16b

Frequency (max)

20MHz

Interface Type

UART

Total Internal Ram Size

2KB

# I/os (max)

39

Number Of Timers - General Purpose

8

Operating Supply Voltage (typ)

3.3/5V

Operating Supply Voltage (max)

5.5V

Operating Supply Voltage (min)

3V

On-chip Adc

12-chx10-bit

Instruction Set Architecture

CISC

Operating Temp Range

-20C to 85C

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

48

Package Type

LQFP

Package

48LQFP

Family Name

R8C

Maximum Speed

20 MHz

Operating Supply Voltage

3.3|5 V

Data Bus Width

16 Bit

Number Of Programmable I/os

39

Number Of Timers

8

For Use With

R0K33026AS000BE - KIT DEV EVALUATION M16C/26A

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

M30260F6AGP#U5AM30260F6AGP#D3

Manufacturer:

Renesas Electronics America

Quantity:

10 000

Part Number:

M30260F6AGP#U5AM30260F6AGP#U3

Manufacturer:

Renesas Electronics America

Quantity:

10 000

Part Number:

M30260F6AGP#U5AM30260F6AGP#U3A

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 232 of 354

- Download datasheet (4Mb)

R

R

M

e

E

15. CRC Calculation Circuit

15.1. CRC Snoop

1

. v

J

Figure 15.1 CRC circuit block diagram

6

0

The Cyclic Redundancy Check (CRC) operation detects an error in data blocks. The microcomputer uses

a generator polynomial of CRC_CCITT (X

CRC code.

The CRC code is a 16-bit code generated for a block of a given data length in multiples of bytes. The code

is updated in the CRC data register everytime one byte of data is transferred to a CRC input register. The

data register needs to be initialized before use. Generation of CRC code for one byte of data is completed

in two machine cycles.

Figure 15.1 shows the block diagram of the CRC circuit. Figure 15.2 shows the CRC-related registers.

Figure 15.3 shows the calculation example using the CRC_CCITT operation.

2

C

9

0 .

B

2 /

0

0

6

The CRC circuit includes the ability to snoop reads and writes to certain SFR addresses. This can be

used to accumulate the CRC value on a stream of data without using extra bandwidth to explicitly write

data into the CRCIN register. All SFR addresses after 0020

snoop is useful to snoop the writes to a UART TX buffer, or the reads from a UART RX buffer.

To snoop an SFR address, the target address is written to the CRC snoop Address Register (bits 9 to

0 in the CRCSAR register). The two most significant bits in this register enable snooping on reads or

writes to the target address. If the target SFR is written to by the CPU or DMA, and the CRC snoop write

bit is set (the CRCSW bit is set to "1"), the CRC will latch the data into the CRCIN register. The new

CRC code will be set in the CRCD register.

Similarly, if the target SFR is read by the CRC or DMA, and the CRC snoop read bit is set (the CRCSR

bit is set to "1"), the CRC will latch the data from the target into the CRCIN register and calculate the

CRC.

The CRC circuit can only calculate CRC codes on data byte at a time. Therefore, if a target SFR is

accessed in a word (16 bit) bus cycle, only the byte of data going to or from the target snooped into

CRCIN, the other byte of the word access is ignored.

2

0

A

F

2

e

G

0 -

b

1 .

o r

2

0

, 5

u

0

p

2

0

(

M

0

7

1

6

CRC input register (8)

C

page 213

x

2 /

16

6

+ x

, A

CRC code generating circuit

12

Data bus high-order

Eight low-order bits

M

Address Bus

Data bus low-order

+ x

1

f o

CRCD register (16)

5

6

+ 1 OR x

3

C

2

2 /

9

6

, B

(Address 03BE

M

16

1

+ x

6

16

C

15

2 /

+ X

+ x

16

6

2

)

) T

12

+ 1

Eight high-order bits

+ X

5

(Address 03BD

+ 1) or CRC-16 (X

16

are subject to the CRC snoop. The CRC

16

, 03BC

16

)

16

Snoop Address

+ X

Equal?

15. CRC Calculation Circuit

15

+ X

2

+ 1) to generate

Snoop

enable

SnoopB

lock

Related parts for M30260F6AGP#U5A

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: