M30280FAHP#D5 Renesas Electronics America, M30280FAHP#D5 Datasheet - Page 101

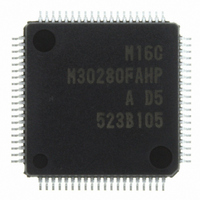

M30280FAHP#D5

Manufacturer Part Number

M30280FAHP#D5

Description

IC M16C MCU FLASH 96K 80-LQFP

Manufacturer

Renesas Electronics America

Series

M16C™ M16C/Tiny/28r

Datasheet

1.M30280F6HPU9.pdf

(425 pages)

Specifications of M30280FAHP#D5

Core Processor

M16C/60

Core Size

16-Bit

Speed

20MHz

Connectivity

I²C, IEBus, SIO, UART/USART

Peripherals

DMA, POR, PWM, Voltage Detect, WDT

Number Of I /o

71

Program Memory Size

96KB (96K x 8)

Program Memory Type

FLASH

Ram Size

8K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 24x10b

Oscillator Type

Internal

Operating Temperature

-20°C ~ 85°C

Package / Case

80-LQFP

For Use With

M30290T2-CPE - EMULATOR COMPACT M16C/26A/28/29M30290T2-CPE-HP - EMULATOR COMPACT FOR M16C/TINY

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Eeprom Size

-

Other names

M30280FAHP#D5A

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 101 of 425

- Download datasheet (4Mb)

M

R

R

e

E

1

. v

Figure 9.8 Operation of Saving Register

J

6

0

C

2

9

2 /

The operation of saving registers carried out in the interrupt sequence is dependent on whether the SP

at the time of acceptance of an interrupt request, is even or odd. If the stack pointer

register and the PC are saved, 16 bits at a time. If odd, they are saved in two steps, 8 bits at a time.

Figure 9.8 shows the operation of the saving registers.

NOTES:

0 .

B

0

0

8

0

1. When any INT instruction in software numbers 32 to 63 has been executed, this is the SP indicated

G

4

J

7

a

o r

by the U flag. Otherwise, it is the ISP.

0 -

. n

u

2

3

p

0

, 1

0

(

M

2

NOTES:

0

1

[SP] – 5 (Odd)

[SP] – 4 (Even)

[SP] – 2 (Even)

(2) SP contains odd number

[SP] – 5 (Even)

[SP] – 3 (Even)

[SP] – 1 (Even)

(1) SP contains even number

[SP] – 3(Odd)

[SP] – 1(Odd)

[SP]

[SP] – 4(Odd)

[SP] – 2(Odd)

[SP]

0

6

7

1. [SP] denotes the initial value of the SP when interrupt request is acknowledged.

C

After registers are saved, the SP content is [SP] minus 4.

2 /

Address

Address

, 8

(Odd)

page 79

(Even)

M

1

6

C

2 /

f o

8

3

) B

FLG

FLG

8

5

Stack

Stack

H

H

FLG

FLG

PC

PC

PC

PC

M

M

L

L

L

L

PC

PC

H

H

Sequence in which order

registers are saved

Sequence in which order

registers are saved

Finished saving registers

in two operations.

(3)

(4)

(1)

(2)

(2) Saved simultaneously,

(1) Saved simultaneously,

Finished saving registers

in four operations.

all 16 bits

all 16 bits

Saved, 8 bits at a time

(1)

is even, the FLG

9. Interrupts

(1)

,

Related parts for M30280FAHP#D5

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: