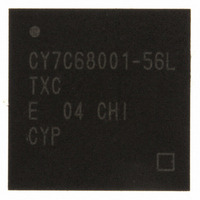

CY7C68001-56LTXC Cypress Semiconductor Corp, CY7C68001-56LTXC Datasheet

CY7C68001-56LTXC

Specifications of CY7C68001-56LTXC

Available stocks

Related parts for CY7C68001-56LTXC

CY7C68001-56LTXC Summary of contents

Page 1

... CY7C68001 EZ-USB SX2™ High-Speed USB Interface Device Cypress Semiconductor Corporation Document #: 38-08013 Rev. *B • 3901 North First Street • CY7C68001 , San Jose CA 95134 • 408-943-2600 Revised July 1, 2003 ...

Page 2

... Standard Enumeration ........................................................................................................... 15 4.2 Default Enumeration ............................................................................................................... 16 5.0 ENDPOINT 0 .................................................................................................................................. 16 6.0 PIN ASSIGNMENTS ...................................................................................................................... 17 6.1 56-pin SSOP ............................................................................................................................ 17 6.2 56-pin QFN ............................................................................................................................... 18 6.3 CY7C68001 Pin Descriptions ................................................................................................. 19 7.0 REGISTER SUMMARY .................................................................................................................. 21 7.1 IFCONFIG Register 0x01 ........................................................................................................ 22 7.1.1 Bit 7: IFCLKSRC ............................................................................................................................ 22 7.1.2 Bit 6: 3048MHZ ..............................................................................................................................22 7.1.3 Bit 5: IFCLKOE ..............................................................................................................................22 Document #: 38-08013 Rev. *B ...

Page 3

... MICROFRAME Registers 0x2C ............................................................................................ 29 7.13 FNADDR Register 0x2D ........................................................................................................ 29 7.14 INTENABLE Register 0x2E ................................................................................................... 29 7.14.1 SETUP Bit 7 ................................................................................................................................. 29 7.14.2 EP0BUF Bit 6 ............................................................................................................................... 29 7.14.3 FLAGS Bit 5 ................................................................................................................................. 29 7.14.4 ENUMOK Bit 2 ............................................................................................................................. 29 7.14.5 BUSACTIVITY Bit 1 ..................................................................................................................... 29 7.14.6 READY Bit 0 ................................................................................................................................. 29 Document #: 38-08013 Rev. *B TABLE OF CONTENTS (continued) CY7C68001 Page ...

Page 4

... DEFAULT DESCRIPTOR ............................................................................................................ 44 13.0 GENERAL PCB LAYOUT GUIDELINES ..................................................................................... 47 14.0 QUAD FLAT PACKAGE NO LEADS (QFN) PACKAGE DESIGN NOTES ................................ 47 15.0 ORDERING INFORMATION ........................................................................................................ 48 16.0 PACKAGE DIAGRAMS ............................................................................................................... 48 16.1 56-pin SSOP Package ........................................................................................................... 48 16.2 56-pin QFN Package ............................................................................................................. 49 17.0 DOCUMENT REVISION HISTORY .............................................................................................. 50 Document #: 38-08013 Rev. *B TABLE OF CONTENTS (continued) CY7C68001 Page ...

Page 5

... FIGURE 1-1. BLOCK DIAGRAM ............................................................................................................ 7 FIGURE 2-1. EXAMPLE USB SYSTEM DIAGRAM ............................................................................... 8 FIGURE 3-1. ENDPOINT CONFIGURATION ....................................................................................... 12 FIGURE 6-1. CY7C68001 56-PIN SSOP PIN ASSIGNMENT .............................................................. 17 FIGURE 6-2. CY7C68001 56-PIN QFN ASSIGNMENT........................................................................ 18 FIGURE 11-1. COMMAND SYNCHRONOUS READ TIMING DIAGRAM............................................ 32 FIGURE 11-2. COMMAND SYNCHRONOUS WRITE TIMING DIAGRAM .......................................... 33 FIGURE 11-3 ...

Page 6

... TABLE 11-16. SLAVE FIFO ASYNCHRONOUS PACKET END STROBE PARAMETERS .............. 39 TABLE 11-17. SLAVE FIFO ASYNCHRONOUS ADDRESS PARAMETERS .................................... 39 TABLE 11-18. SLAVE FIFO ADDRESS TO FLAGS/DATA PARAMETERS ...................................... 39 TABLE 11-19. SLAVE FIFO OUTPUT ENABLE PARAMETERS ....................................................... 40 TABLE 15-1. ORDERING INFORMATION .......................................................................................... 48 Document #: 38-08013 Rev. *B LIST OF TABLES CY7C68001 Page ...

Page 7

... Document #: 38-08013 Rev. *B SCL I2C Bus Controller (Master Only) SDA PLL SX2 Internal Logic CY Smart USB USB 2.0 XCVR FS/HS Engine Figure 1-1. Block Diagram CY7C68001 IFCLK* Read*, Write*, OE*, PKTEND*, CS# Interrupt#, Ready Flags (3/4) Address (3) Control FIFO Data 8/16-Bit Data Bus 4 KB ...

Page 8

... Please see the Cypress web site at www.cypress.com. 2.1 System Diagram Document #: 38-08013 Rev indows apable H ost able onnection C ypress / evice pplication Figure 2-1. Example USB System Diagram CY7C68001 Page ...

Page 9

... The SCL and SDA pins must be pulled up for this detection method to work properly, even if an EEPROM is not connected. Typical pull-up values are 2.2K – 10K Ohms. Document #: 38-08013 Rev. *B CY7C68001 2 C-compatible EEPROM. Table 3-2. Descriptor Length Not Set to 0x06 Byte Index ...

Page 10

... If this interrupt is enabled and the SX2 receives a SET_CONFIGURATION request from the USB host, the SX2 asserts the INT# pin and sets bit 2 in the Interrupt Status Byte. This event signals the completion of the SX2 enumeration process. Document #: 38-08013 Rev. *B CY7C68001 Page ...

Page 11

... EP0–Bidirectional Endpoint 0, 64-byte buffer. • EP2 8–Eight 512-byte buffers, bulk, interrupt, or isochronous. EP2 and EP6 can be either double-, triple-, or quad- buffered. EP4 and EP8 can only be double-buffered. For high-speed endpoint configuration options, see Figure 3-1. Document #: 38-08013 Rev. *B CY7C68001 has reached 3.3V. Typically, CC Page ...

Page 12

... READY signal for gating writes, and an INT# signal to indicate that the SX2 has data to be read, or that an interrupt event has occurred. The command interface uses the same control signals (IFCLK, CS#, SLRD, SLWR, SLOE, and FIFOADR[2:0]) as the FIFO interface, except for PKTEND. Document #: 38-08013 Rev Figure 3-1. Endpoint Configuration CY7C68001 Page ...

Page 13

... WORDWIDE bit in the EPxPKTLENH/L registers. The data bus is bidirectional, with its output drivers controlled by the SLOE pin. The FIFOADR[2:0] pins select which of the four FIFOs is connected to the FD [15:0] bus the command interface is selected. Document #: 38-08013 Rev. *B FIFOADR2 FIFOADR1 CY7C68001 FIFOADR0 Page ...

Page 14

... The first command data byte contains the upper nibble of data, and the second command byte contains the lower nibble of data. Note indexed mode, the value of the FLAGx pins is indeterminate except when addressing a FIFO (FIFOADR[2:0]={000,001,010,011}). Document #: 38-08013 Rev Bit 5 Bit 4 Bit 3 Bit 5 Bit 4 Bit Bit 5 Bit 4 Bit CY7C68001 [ Bit 2 Bit 1 Bit 0 Bit 2 Bit 1 Bit Bit 2 Bit 1 Bit Page ...

Page 15

... Section 3.4 is asserted, the SX2 will buffer that interrupt until the read request completes. 5. These and all other data bytes must conform to the command protocol. Document #: 38-08013 Rev Don’t Care Don’t Care Don’t Care Don’t Care [5] [5] Note: the register address is only written once. CY7C68001 Page ...

Page 16

... The SX2 will not allow more data than the wLength field specified in the set-up packet. Note: the PKTEND pin does not apply to Endpoint 0. The only way to send a short or zero length packet is by writing to the byte count register with the appropriate value. Document #: 38-08013 Rev. *B CY7C68001 Page ...

Page 17

... If the SX2 receives a set-up packet with no data phase, the external master can accept the packet and complete the handshake phase by writing zero to the byte count register. 6.0 Pin Assignments 6.1 56-pin SSOP Figure 6-1. CY7C68001 56-pin SSOP Pin Assignment Note denotes programmable polarity. Document #: 38-08013 Rev. *B FD13 ...

Page 18

... QFN *SLRD 1 *SLWR 2 AVCC 3 XTALOUT 4 XTALIN 5 AGND 6 VCC 7 DPLUS 8 DMINUS 9 GND 10 VCC 11 GND 12 *IFCLK 13 RESERVED 14 Figure 6-2. CY7C68001 56-pin QFN Assignment Document #: 38-08013 Rev. *B CY7C68001 56-pin QFN [6] CY7C68001 42 RESET# 41 GND 40 *FLAGD/CS# 39 *PKTEND 38 FIFOADR1 37 FIFOADR0 36 FIFOADR2 35 *SLOE 34 INT# 33 READY 32 VCC 31 *FLAGC ...

Page 19

... CY7C68001 Pin Descriptions Table 6-1. SX2 Pin Descriptions QFN SSOP Pin Pin Name Type 3 10 AVCC Power 6 13 AGND Power 9 16 DMINUS I/O DPLUS I/O RESET# Input 5 12 XTALIN Input 4 11 XTALOUT Output Output 33 40 READY Output 34 41 INT# Output ...

Page 20

... Connect to 3.3V power source Connect to 3.3V power source Connect to 3.3V power source. CC N/A Connect to ground. N/A Connect to ground. N/A Connect to ground. N/A Connect to ground. N/A Connect to ground. N/A Connect to ground. N/A Connect to ground. CY7C68001 Description with a 2.2K-10 K Ohms resistor, even EEPROM Page ...

Page 21

... FC7 FC6 FC5 FC4 FC3 HSGRANT FA6 FA5 FA4 FA3 SETUP EP0BUF FLAGS CY7C68001 Default STANDBY FLAGD/CS# DISCON 11001001 FLAGA2 FLAGA1 FLAGA0 00000000 FLAGC2 FLAGC1 FLAGC0 00000000 SLWR EF FF 00000000 minor minor minor xxxxxxxx STALL BUF1 BUF0 10100010 0 STALL 0 0 10100000 ...

Page 22

... The SX2 has four FIFO flags output pins: FLAGA, FLAGB, FLAGC, FLAGD. FLAGSAB Bit # 7 6 Bit Name FLAGB3 FLAGB2 Read/Write R/W R/W Reset 0 0 Document #: 38-08013 Rev IFCLKOE IFCLKPOL ASYNC R/W R/W R FLAGB1 FLAGB0 FLAGA3 R/W R/W R CY7C68001 0x01 STANDBY FLAGD/CS# DISCON R/W R/W R 0x02 FLAGA2 FLAGA1 FLAGA0 R/W R/W R Page ...

Page 23

... FIFO is selected by FIFOADR[2:0] pins Reserved 1 0 Reserved 1 1 Reserved 0 0 EP2 EP4 EP6 EP8 EP2 EP4 EP6 EP8 EP2 EP4 EP6 EP8 PKTEND SLOE R/W R CY7C68001 FLAGC2 FLAGC1 R/W R/W R Pin Function SLRD SLWR EF R/W R/W R 0x03 0 FLAGC0 R/W 0 0x04 0 FF R/W 0 Page ...

Page 24

... These bits define the endpoint type, as shown in Table 7-3. The TYPE bits apply to all of the endpoint configuration registers. All SX2 endpoints except EP0 default to BULK. Document #: 38-08013 Rev Major Major Minor R/W R/W R TYPE1 TYPE0 SIZE R/W R/W R CY7C68001 0x05 Minor Minor Minor R/W R/W R 0x06, 0x07, 0x08, 0x09 STALL BUF1 BUF0 R/W R/W R ...

Page 25

... PL4 PL3 R/W R/W R ZEROLEN WORDWIDE 0 R/W R/W R ZEROLEN WORDWIDE 0 R/W R/W R CY7C68001 Endpoint Type Invalid Isochronous Bulk (Default) Interrupt Buffering Quad Invalid Double Triple 0x0B, 0x0D, 0x0F, 0x11 PL2 PL1 PL0 R/W R/W R 0x0A, 0x0E PL10 PL9 PL8 R/W R/W ...

Page 26

... PFC4 PFC3 R/W R/W R INPKTS[2] INPKTS[1] INPKTS[0] OUT:PFC12 OUT:PFC11 OUT:PFC10 R/W R/W R INPKTS[2] INPKTS[1] INPKTS[0] OUT:PFC12 OUT:PFC11 OUT:PFC10 R/W R/W R CY7C68001 0x13, 0x15, 0x17, 0x19 PFC2 PFC1 PFC0 R/W R/W R 0x12, 0x16 PFC8 R/W R/W R 0x14, 0x18 PFC8 R/W R/W R/W 0 ...

Page 27

... EP4PF Read/Write R/W R/W Reset 0 0 Document #: 38-08013 Rev applies to PKTS1 PKTS0 R/W R INPPF0 EP4EF EP4FF R/W R CY7C68001 EPnPFH:L format PKTS[] PFC[] PFC[] Number of packets 0x1A, 0x1B, 0x1C, 0x1D INPPF2 INPPF1 R/W R/W R Packets Invalid 1 (default EP2PF EP4EF R/W R/W R INPPF0 ...

Page 28

... One use of the frame count is to respond to the USB SYNC_FRAME Request. If the SX2 detects a missing or garbled SOF, the SX2 generates an internal SOF and increments USBFRAMEL–USBRAMEH. Document #: 38-08013 Rev EP8EF EP8FF 0 R/W R/W R FIFO4 FIFO2 EP3 FC5 FC4 FC3 CY7C68001 0x1F EP6PF EP6EF EP6FF R/W R/W R 0x20 EP2 EP1 EP0 0x2A FC10 FC9 FC8 0x2B FC2 FC1 FC0 ...

Page 29

... READY Bit 0 Setting this bit enables an interrupt when the SX2 has powered on and performed an internal self-test. Document #: 38-08013 Rev FA5 FA4 FA3 FLAGS ENUMOK 1 R/W R/W R CY7C68001 0x2C MF2 MF1 MF0 0x2D FA2 FA1 FA0 0x2E BUSACTIVITY READY R/W R/W R ...

Page 30

... USB host. For Endpoint 0 IN transfers, the external master writes the number of bytes in the Endpoint 0 buffer to transfer the bytes to the USB host. For complete details, refer to Section 5.0. Document #: 38-08013 Rev. *B CY7C68001 Page ...

Page 31

... Conditions 0< V < OUT I = –4 mA OUT Except D+/D- D+/D- includes 1.5k integrated pull-up excluding 1.5k integrated pull-up Connected to USB at high speed Connected to USB at full speed Vcc min = 3.0V CY7C68001 Min. Typ. Max. Unit 3.0 3.3 3 5.25 V –0.5 0.8 V ±10 A 2.4 V 0.4 ...

Page 32

... Clock to Command Data Output Propagation Delay XFD Notes: 8. Dashed lines denote signals with programmable polarity. 9. Externally sourced IFCLK must not exceed 50 MHz. Document #: 38-08013 Rev IFCLK t RDH t SRD t INT N OEon XFD Description [9] Description CY7C68001 t OEoff [8] Min. Max. Unit 20. 10.5 ns 10 Min. Max. Unit 20 ...

Page 33

... Clock to Command Data Hold Time FDH t Clock to READY Output Propagation Time NRDY Document #: 38-08013 Rev IFCLK t t SWR WRH t t SFD FDH NRDY Description Description CY7C68001 Z t NRDY [8] Min. Max. 20.83 18.1 0 9.2 0 9.5 [9] Min. Max. 20 200 12.1 3.6 3.2 4.5 13 ...

Page 34

... Command DATA to SLWR Hold Time FDH t READY to SLWR Time RDYWR t SLWR to READY RDY Document #: 38-08013 Rev RDpwl t XINT t XFD t IRD N N+1 t OEon Description t t WRpwh WRpwl t t FDH SFD t RDY t NRDY Description CY7C68001 t RDpwh t OEoff [8] Min. Max 10.5 10.5 [8] Min. Max Page Unit Unit ns ...

Page 35

... OEoff t Clock to FLAGS Output Propagation Delay XFLG t Clock to FIFO Data Output Propagation Delay XFD Document #: 38-08013 Rev IFCLK t t RDH SRD t XFLG N N OEon XFD [9] Description [9] Description CY7C68001 t OEoff [8] Min. Max. Unit 20. 10.5 ns 10 Min. Max. Unit 20 200 ns 12 ...

Page 36

... FIFO Data to Clock Set-up Time SFD t Clock to FIFO Data Hold Time FDH t Clock to FLAGS Output Propagation Time XFLG Document #: 38-08013 Rev IFCLK t WRH t SWR SFD FDH t XFLG Description Description CY7C68001 Z [8] [9] Min. Max. Unit 20. 9.5 ns [9] Min. Max. Unit ...

Page 37

... Interface Clock Period IFCLK t FIFOADR[2:0] to Clock Set-up Time SFA t Clock to FIFOADR[2:0] Hold Time FAH Document #: 38-08013 Rev PEH t SPE t XFLG Description Description t t SFA FAH [9] Description CY7C68001 [8] [9] Min. Max. Unit 20. 9.5 ns [9] Min. Max. Unit 20 200 ns 8 ...

Page 38

... XFD Note: 10. Slave FIFO asynchronous parameter values are using internal IFCLK setting at 48 MHz. Document #: 38-08013 Rev RDpwh t RDpwl t XFLG t XFD N N OEon OEoff [10] Description t WRpwh t WRpwl t SFD t FDH t XFD Description CY7C68001 [8] Min. Max. Unit 10.5 ns 10.5 ns [8] [10] Min. Max. Unit ...

Page 39

... This is yet to be characterized. We recommend that you use a 70 ns. Document #: 38-08013 Rev PEpwh t PEpwl t XFLG [10] Description t FAH t SFA [10] Description t XFLG t XFD N N+1 Description CY7C68001 Min. Max. Unit [8] Min. Max. Unit [11] TBD ns [8] Min. ...

Page 40

... XFD XFD N+2 N+1 N OEon OEoff IFCLK IFCLK IFCLK N+1 N+1 N+1 SLOE SLRD SLOE SLRD Not Driven N+1 N+1 CY7C68001 t OEoff [8] Min. Max. 10.5 10.5 t FAH >= t RDH t t XFD XFD N+4 N+3 t OEoff IFCLK IFCLK IFCLK IFCLK N+4 ...

Page 41

... FIFO address lines need to be set up a clock cycle SFA before the rising edge of the IFCLK to meet the data setup time. SFD measured from the rising edge of IFCLK. If SLCS is used then, SLCS must WRH CY7C68001 from the rising edge of SRD from the rising edge of the IFCLK the above t FAH > ...

Page 42

... Document #: 38-08013 Rev SFA t t RDpwl RDpwh t XFLG t XFD N N OEon OEoff SLRD SLOE SLOE N+1 N+1 N N+1 Not Driven CY7C68001 t FAH RDpwl RDpwh RDpwl RDpwh t XFLG t t XFD XFD N+3 N+2 t OEoff SLRD SLOE SLRD SLRD SLRD N+2 N+3 N+1 ...

Page 43

... Document #: 38-08013 Rev SFA WRpwl WRpwh WRpwl WRpwh SFD FDH SFD FDH N+1 N+2 before the deasserting edge of the SLWR to meet the data setup time. SFD CY7C68001 t FAH t t WRpwl WRpwh t XFLG t t SFD FDH N PEpwl PEpwh [8] SFA. and minimum WRpwl Page ...

Page 44

... Descriptor 7, //Descriptor length 5, //Descriptor type 0x02, //Endpoint number, and direction 2, //Endpoint type 0x00, //Maximum packet size (LSB) 0x02, //Max packet size (MSB) 0x00, //Polling interval Document #: 38-08013 Rev. *B CY7C68001 Page ...

Page 45

... Descriptor 7, //Descriptor length 5, //Descriptor type 0x02, //Endpoint number, and direction 2, //Endpoint type 0x40, //Maximum packet size (LSB) 0x00, //Max packet size (MSB) 0x00, //Polling interval Document #: 38-08013 Rev. *B CY7C68001 Page ...

Page 46

... Descriptor ’C’,00, ’Y’,00, ’7’,00, ’C’,00, ’6’,00, ’8’,00, ’0’,00, ’0’,00, ’1’,00, Document #: 38-08013 Rev. *B //US LANGID Code CY7C68001 Page ...

Page 47

... Document #: 38-08013 Rev. *B [2] 0.017” dia Solder Mask Cu Fill Cu Fill 0.013” dia PCB Material This figure only shows the top three layers of the circuit board: Top Solder, PCB Dielectric, and the Ground Plane. Figure 0-1. (b) X-ray Image of the Assembly CY7C68001 Page ...

Page 48

... SSOP Package Figure 16-1. 56-lead Shrunk Small Outline Package Note: 3. Slave FIFO asynchronous parameter values are using internal IFCLK setting at 48 MHz. Document #: 38-08013 Rev SSOP 56 QFN EZ-USB SX2 Development Kit 56-pin Shrunk Small Outline Package 056 CY7C68001 Package Type 51-85062-*C Page ...

Page 49

... Semiconductor products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress Semiconductor against all charges. 56-Lead QFN LF56A Figure 16-2. LF56A 56-pin QFN Package 2 C system, provided that the system conforms to the I CY7C68001 51-85144-* Standard Specification Page ...

Page 50

... Document Revision History Description Title: CY7C68001 EZ-USB SX2™ High-Speed USB Interface Device Document Number: 38-08013 Orig. of REV. ECN No. Issue Date Change ** 111807 06/07/02 *A 123155 02/07/03 *B 126324 07/02/03 MON Document #: 38-08013 Rev. *B BHA New Data Sheet BHA Minor clean-up and clarification ...