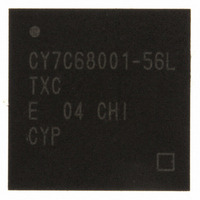

CY7C68001-56LTXC Cypress Semiconductor Corp, CY7C68001-56LTXC Datasheet - Page 7

CY7C68001-56LTXC

Manufacturer Part Number

CY7C68001-56LTXC

Description

IC USB EZ-USB SX2 HS 56VQFN

Manufacturer

Cypress Semiconductor Corp

Series

CY7Cr

Type

USBr

Specifications of CY7C68001-56LTXC

Protocol

USB 2.0

Voltage - Supply

3 V ~ 3.6 V

Mounting Type

Surface Mount

Package / Case

56-VQFN Exposed Pad, 56-HVQFN, 56-SQFN, 56-DHVQFN

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Drivers/receivers

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

428-2932

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

CY7C68001-56LTXC

Manufacturer:

CYPRESS/赛普拉斯

Quantity:

20 000

1.0

1.1

The EZ-USB SX2

cessors, DSPs, ASICs, and FPGAs to enable USB 2.0 support for any peripheral design. SX2 has a built-in USB trans-

ceiver and Serial Interface Engine (SIE), along with a command decoder for sending and receiving USB data. The

controller has four endpoints that share a 4-KB FIFO space for maximum flexibility and throughput, as well as Control

Endpoint 0. SX2 has three address pins and a selectable 8- or 16- bit data bus for command and data input or output.

1.2

1.3

Document #: 38-08013 Rev. *B

• USB 2.0-certified compliant

• Operates at high (480 Mbps) or full (12 Mbps) speed

• Supports Control Endpoint 0:

• Supports four configurable endpoints that share a 4-KB FIFO space

• Standard 8- or 16-bit external master interface

• Integrated phase-locked loop (PLL)

• 3.3V operation, 5V tolerant I/Os

• 56-pin SSOP and QFN package

• Complies with most device class specifications

— Used for handling USB device requests

— Endpoints 2, 4, 6, 8 for application-specific control and data

— Glueless interface to most standard microprocessors DSPs, ASICs, and FPGAs

— Synchronous or Asynchronous interface

Introduction

Features

Block Diagram

EZ-USB SX2™ Features

DMINUS

24 MHz

DPLUS

XTAL

USB interface device is designed to work with any external master, such as standard micropro-

VCC

1.5K

USB 2.0 XCVR

SCL

SDA

PLL

Figure 1-1. Block Diagram

CY Smart USB

FS/HS Engine

(Master Only)

Controller

I2C Bus

SX2 Internal Logic

FIFO

4 KB

Read*, Write*, OE*, PKTEND*, CS#

Control

Data

Interrupt#, Ready

Address (3)

Flags (3/4)

FIFO

IFCLK*

Data

Bus

8/16-Bit Data

CY7C68001

Page 7 of 50