DS2156L+ Maxim Integrated Products, DS2156L+ Datasheet - Page 11

DS2156L+

Manufacturer Part Number

DS2156L+

Description

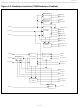

IC TXRX T1/E1/J1 1-CHIP 100-LQFP

Manufacturer

Maxim Integrated Products

Datasheet

1.DS2156L.pdf

(265 pages)

Specifications of DS2156L+

Function

Single-Chip Transceiver

Interface

E1, J1, T1, TDM, UTOPIA II

Number Of Circuits

1

Voltage - Supply

3.14 V ~ 3.47 V

Current - Supply

75mA

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

100-LQFP

Includes

BERT Generator and Detector, CMI Coder and Decoder, HDLC Controller

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Power (watts)

-

- Current page: 11 of 265

- Download datasheet (2Mb)

Extended System Information Bus

User-Programmable Output Pins

The DS2156 is compliant with the following standards:

ANSI:

AT&T:

ITU:

ITU-T:

ETSI:

Japanese:

ATM Forum:

ATM Forum:

ATM Forum:

Loopbacks: remote, local, analog, and per-channel

loopback

Host can read interrupt and alarm status on up to 8

ports with a single bus read

Four user-defined output pins for controlling

external logic

T1.403-1995, T1.231–1993, T1.408

TR54016, TR62411

G.703, G.704, G.706, G.736, G.775, G.823, G.932, I.431, O.151, Q.161

Recommendation I.432–03/93 B-ISDN User-Network Interface—Physical Layer

Specification

ETS 300 011, ETS 300 166, ETS 300 233, CTR12, CTR4

JTG.703, JTI.431, JJ-20.11 (CMI Coding Only)

“DS1 Physical Layer Specification,” af-phy-0016.000, September 1994

“E1 Physical Layer Specification,” af-phy-0064.000, September 1996

“UTOPIA Level 2 Specification,” Version 1.0, af-phy-0039.000, June 1995

11 of 265

Control Port

8-bit parallel control port

Multiplexed or nonmultiplexed buses

Intel or Motorola formats

Supports polled or interrupt environments

Software access to device ID and silicon revision

Software reset supported

–

Hardware reset pin

Automatic clear on power-up

Related parts for DS2156L+

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Ds2156, Ds2156l, Ds2156ln T1/e1/j1 Single-chip Transceiver Tdm/utopia Ii Interface

Manufacturer:

Maxim Integrated Products, Inc.

Datasheet:

Part Number:

Description:

MAX7528KCWPMaxim Integrated Products [CMOS Dual 8-Bit Buffered Multiplying DACs]

Manufacturer:

Maxim Integrated Products

Datasheet:

Part Number:

Description:

Single +5V, fully integrated, 1.25Gbps laser diode driver.

Manufacturer:

Maxim Integrated Products

Datasheet:

Part Number:

Description:

Single +5V, fully integrated, 155Mbps laser diode driver.

Manufacturer:

Maxim Integrated Products

Datasheet:

Part Number:

Description:

VRD11/VRD10, K8 Rev F 2/3/4-Phase PWM Controllers with Integrated Dual MOSFET Drivers

Manufacturer:

Maxim Integrated Products

Datasheet:

Part Number:

Description:

Highly Integrated Level 2 SMBus Battery Chargers

Manufacturer:

Maxim Integrated Products

Datasheet:

Part Number:

Description:

Current Monitor and Accumulator with Integrated Sense Resistor; ; Temperature Range: -40°C to +85°C

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

TSSOP 14/A�/RS-485 Transceivers with Integrated 100O/120O Termination Resis

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

TSSOP 14/A�/RS-485 Transceivers with Integrated 100O/120O Termination Resis

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

QFN 16/A�/AC-DC and DC-DC Peak-Current-Mode Converters with Integrated Step

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

TDFN/A/65V, 1A, 600KHZ, SYNCHRONOUS STEP-DOWN REGULATOR WITH INTEGRATED SWI

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Integrated Temperature Controller f

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

SOT23-6/I�/45MHz to 650MHz, Integrated IF VCOs with Differential Output

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

SOT23-6/I�/45MHz to 650MHz, Integrated IF VCOs with Differential Output

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

EVALUATION KIT/2.4GHZ TO 2.5GHZ 802.11G/B RF TRANSCEIVER WITH INTEGRATED PA

Manufacturer:

Maxim Integrated Products