ADUC7121BBCZ-RL Analog Devices Inc, ADUC7121BBCZ-RL Datasheet - Page 16

ADUC7121BBCZ-RL

Manufacturer Part Number

ADUC7121BBCZ-RL

Description

PRECISION ANALOG MCU I.C

Manufacturer

Analog Devices Inc

Series

MicroConverter® ADuC7xxxr

Datasheet

1.ADUC7121BBCZ.pdf

(96 pages)

Specifications of ADUC7121BBCZ-RL

Core Processor

ARM7

Core Size

16/32-Bit

Speed

41.78MHz

Connectivity

I²C, SPI, UART/USART

Peripherals

POR, PWM, WDT

Number Of I /o

32

Program Memory Size

126KB (63K x 16)

Program Memory Type

FLASH

Ram Size

8K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 3.6 V

Data Converters

A/D 9x12b, D/A 4x12b

Oscillator Type

Internal

Operating Temperature

-10°C ~ 95°C

Package / Case

108-LFBGA, CSPBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

ADUC7121BBCZ-RL

ADUC7121BBCZ-RLTR

ADUC7121BBCZ-RLTR

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ADUC7121BBCZ-RL

Manufacturer:

Analog Devices Inc

Quantity:

10 000

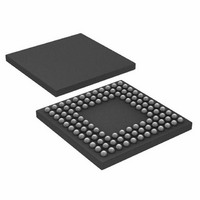

ADuC7121

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Table 9. Pin Function Descriptions

Pin No.

C12

D11

E11

C3

D3

E3

F3

G3

G10

Mnemonic

RST

P0.0/SCL0/PLAI[5]

P0.1/SDA0/PLAI[4]

P0.2/SPICLK/ADC

P0.3/MISO/PLAO[12]/SYNC

P0.4/MOSI/PLAI[11]/TRIP

P0.5/CS/PLAI[10]/ADC

P0.6/MRST/PLAI[2]

P0.7/TRST/PLAI[3]

BUSY

/PLAO[13]

CONVST

Type

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

G

M

A

B

C

D

E

H

K

F

J

L

1

1

1

Description

Reset Input (Active Low).

I

Programmable Logic Array for Input Element 5 (PLAI[5]).

I

Programmable Logic Array for Input Element 4 (PLAI[4]).

SPI Clock (SPICLK).

Status of the ADC (ADC

Programmable Logic Array for Output Element 13 (PLAO[13]).

SPI Master In Slave Out (MISO).

Programmable Logic Array for Output Element 12 (PLAO[12]).

Synchronous Reset (SYNC). Input to reset synchronously the PWM counters using an

external source.

General-Purpose Input and Output Port 0.4 (P0.4).

SPI Master Out Slave In (MOSI).

Programmable Logic Array for Input Element 11 (PLAI[11]).

PWM Trip Interrupt (TRIP). The TRIP function of Pin E3 is the input that allows the PWM

trip interrupt to be triggered.

SPI Slave Select Input (CS).

Programmable Logic Array for Input Element 10 (PLAI[10]).

ADC Conversions (ADC

conversions using the PLA or the timer output.

Power On Reset Output (MRST).

Programmable Logic Array for Input Element 2 (PLAI[2]).

JTAG Test Port Input, Test Reset (TRST). Debug and download access.

Programmable Logic Array for Input Element 3 (PLAI[3]).

2

General-Purpose Input and Output Port 0.0 (P0.0).

General-Purpose Input and Output Port 0.1 (P0.1).

General-Purpose Input and Output Port 0.2 (P0.2).

General-Purpose Input and Output Port 0.3 (P0.3).

General-Purpose Input and Output Port 0.5 (P0.5).

General-Purpose Input and Output Port 0.6 (P0.6).

General-Purpose Input and Output Port 0.7 (P0.7).

2

2

2

C Interface Serial Clock for I

C Interface Serial Data for I

3

3

Figure 7. Pin Configuration

4

4

Rev. 0 | Page 16 of 96

5

ADuC7121

5

TOP VIEW

6

6

7

7

8

8

9 10 11 12

9 10 11 12

CONVST

BUSY

).

). The ADC

2

2

C0 (SDA0).

C0 (SCL0).

A

B

C

D

E

F

G

H

J

K

L

M

CONVST

function of Pin F3 initiates the ADC