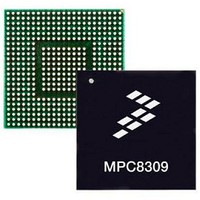

MPC8309VMAHFCA Freescale Semiconductor, MPC8309VMAHFCA Datasheet - Page 31

MPC8309VMAHFCA

Manufacturer Part Number

MPC8309VMAHFCA

Description

417/333/233 MP Std Tmp

Manufacturer

Freescale Semiconductor

Datasheet

1.MPC8309VMAHFCA.pdf

(81 pages)

Specifications of MPC8309VMAHFCA

Processor Series

MPC8309

Core

e300c3

Data Bus Width

32 bit

Data Ram Size

512 MB

Interface Type

USB, CAN, UART, PCI

Maximum Clock Frequency

417 MHz

Number Of Programmable I/os

56

Operating Supply Voltage

- 0.3 V to + 1.26 V

Maximum Operating Temperature

+ 105 C

Mounting Style

SMD/SMT

Operating Temperature Range

0 C to + 105 C

Processor To Be Evaluated

MPC8309

Supply Current (max)

5 uA

Lead Free Status / Rohs Status

Details

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MPC8309VMAHFCA

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

9.2

The following table provides the TDM/SI input and output AC timing specifications.

The following figure provides the AC test load for the TDM/SI.

The following figure represents the AC timing from

generally reference the rising edge of the clock, these AC timing diagrams also apply when the falling edge

is the active edge.

10 HDLC

This section describes the DC and AC electrical specifications for the high level data link control (HDLC),

of the MPC8309.

Freescale Semiconductor

TDM/SI outputs—External clock delay

TDM/SI outputs—External clock High Impedance

TDM/SI inputs—External clock input setup time

TDM/SI inputs—External clock input hold time

Notes:

1. Output specifications are measured from the 50% level of the rising edge of QE_CLK_IN to the 50% level of the signal.

2. The symbols used for timing specifications follow the pattern of t

Timings are measured at the pin.

inputs and t

outputs external timing (SE) for the time t

are invalid (X).

MPC8309 PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

TDM/SICLK (Input)

Note: The clock edge is selectable on TDM/SI.

TDM/SI AC Timing Specifications

Output Signals:

(first two letters of functional block)(reference)(state)(signal)(state)

Input Signals:

(See Note)

(See Note)

TDM/SI

TDM/SI

Characteristic

Output

Figure 21. TDM/SI AC Timing (External Clock) Diagram

t

SEIVKH

Table 29. TDM/SI AC Timing Specifications

TDM/SI

Figure 20. TDM/SI AC Test Load

Z

0

memory clock reference (K) goes from the high state (H) until outputs (O)

= 50

t

SEKHOX

t

SEKHOV

Table

t

SEIXKH

(first two letters of functional block)(signal)(state)(reference)(state)

for outputs. For example, t

29. Note that although the specifications

Symbol

t

t

t

t

SEKHOV

SEKHOX

SEIVKH

SEIXKH

R

L

= 50

2

1

OV

Min

2

2

5

2

DD

SEKHOX

/2

symbolizes the TDM/SI

Max

14

10

—

—

Unit

ns

ns

ns

ns

for

HDLC

31