MPC8313E-RDB Freescale Semiconductor, MPC8313E-RDB Datasheet - Page 81

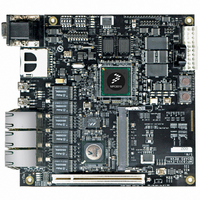

MPC8313E-RDB

Manufacturer Part Number

MPC8313E-RDB

Description

BOARD PROCESSOR

Manufacturer

Freescale Semiconductor

Series

PowerQUICC II™ PROr

Type

MCUr

Datasheets

1.MPC8313CZQAFFB.pdf

(100 pages)

2.MPC8313E-RDBB.pdf

(52 pages)

3.MPC8313E-RDBB.pdf

(2 pages)

Specifications of MPC8313E-RDB

Contents

Reference Design Board, Software and Documentation

Termination Type

SMD

Supply Voltage Max

1.05V

Tool / Board Applications

Wired Connectivity-LIN, CAN, Ethernet, USB

Mcu Supported Families

POWERQUICC II PRO

Rohs Compliant

Yes

Filter Terminals

SMD

Silicon Manufacturer

Freescale

Silicon Core Number

MPC83xx

Kit Application Type

Communication & Networking

Application Sub Type

Ethernet

Core Architecture

Power Architecture

Silicon Family Name

PowerQUICC II PRO

For Use With/related Products

MPC8313E

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

20.2

RCWL[COREPLL] selects the ratio between the internal coherent system bus clock (csb_clk) and the e300

core clock (core_clk).

not listed in

Freescale Semiconductor

1

2

For core_clk:csb_clk ratios of 2.5:1 and 3:1, the core_clk must not exceed its maximum operating frequency of

333 MHz.

Core VCO frequency = core frequency × VCO divider. Note that VCO divider has to be set properly so that the core

VCO frequency is in the range of 400–800 MHz.

0–1

nn

11

00

01

10

00

01

10

00

01

10

00

01

10

00

01

10

Core PLL Configuration

RCWL[COREPLL]

Table 68

Core VCO frequency = core frequency × VCO divider. The VCO divider,

which is determined by RCWLR[COREPLL], must be set properly so that

the core VCO frequency is in the range of 400–800 MHz.

nnnn

0000

0001

0001

0001

0001

0001

0001

0010

0010

0010

0010

0010

0010

0011

0011

0011

2–5

MPC8313E PowerQUICC

should be considered as reserved.

Table 68

6

0

n

0

0

0

1

1

1

0

0

0

1

1

1

0

0

0

shows the encodings for RCWL[COREPLL]. COREPLL values that are

(PLL off, csb_clk clocks core directly)

Table 68. e300 Core PLL Configuration

core_clk : csb_clk Ratio

™

II Pro Processor Hardware Specifications, Rev. 3

PLL bypassed

1.5:1

1.5:1

1.5:1

2.5:1

2.5:1

2.5:1

n/a

1:1

1:1

1:1

2:1

2:1

2:1

3:1

3:1

3:1

NOTE

1

(PLL off, csb_clk clocks core directly)

VCO Divider (VCOD)

PLL bypassed

n/a

2

4

8

2

4

8

2

4

8

2

4

8

2

4

8

2

Clocking

81