PIC16F1824-I/P Microchip Technology, PIC16F1824-I/P Datasheet - Page 413

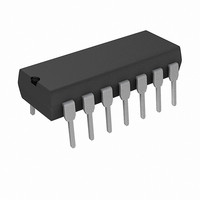

PIC16F1824-I/P

Manufacturer Part Number

PIC16F1824-I/P

Description

IC PIC MCU 8BIT 14KB FLSH 14PDIP

Manufacturer

Microchip Technology

Series

PIC® XLP™ 16Fr

Datasheets

1.PIC16F722-ISS.pdf

(8 pages)

2.PIC16F1824-ISL.pdf

(2 pages)

3.PIC16F1824-ISL.pdf

(419 pages)

4.PIC16F1824-ISL.pdf

(10 pages)

5.PIC16F1824-IP.pdf

(10 pages)

Specifications of PIC16F1824-I/P

Core Processor

PIC

Core Size

8-Bit

Speed

32MHz

Connectivity

I²C, SPI, UART/USART

Peripherals

Brown-out Detect/Reset, POR, PWM, WDT

Number Of I /o

11

Program Memory Size

7KB (4K x 14)

Program Memory Type

FLASH

Eeprom Size

256 x 8

Ram Size

256 x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

14-DIP (0.300", 7.62mm)

Processor Series

PIC16F

Core

PIC

3rd Party Development Tools

52715-96, 52716-328, 52717-734

Development Tools By Supplier

PG164130, DV164035, DV244005, DV164005

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

- PIC16F722-ISS PDF datasheet

- PIC16F1824-ISL PDF datasheet #2

- PIC16F1824-ISL PDF datasheet #3

- PIC16F1824-ISL PDF datasheet #4

- PIC16F1824-IP PDF datasheet #5

- Current page: 413 of 419

- Download datasheet (4Mb)

PIC16(L)F1824/1828

SSPxSTAT Register.......................................................... 292

Stack ................................................................................... 45

Stack Overflow/Underflow................................................... 82

STATUS Register................................................................ 26

SUBWFB........................................................................... 349

T

T1CON Register.......................................................... 33, 197

T1GCON Register............................................................. 198

T2CON Register.................................................................. 33

T4CON Register.................................................................. 41

T6CON Register.................................................................. 41

Temperature Indicator Module .......................................... 147

Thermal Considerations .................................................... 364

Timer0 ............................................................................... 185

Timer1 ............................................................................... 189

Timer2

Timer2/4/6 ......................................................................... 201

Timers

Timing Diagrams

DS41419B-page 412

R/W Bit ...................................................................... 260

Accessing.................................................................... 45

Reset........................................................................... 47

Associated Registers ................................................ 187

Operation .................................................................. 185

Specifications ............................................................ 372

Associated registers.................................................. 199

Asynchronous Counter Mode ................................... 191

Clock Source Selection ............................................. 190

Interrupt..................................................................... 193

Operation .................................................................. 190

Operation During Sleep ............................................ 193

Oscillator ................................................................... 191

Prescaler ................................................................... 191

Specifications ............................................................ 372

Timer1 Gate

TMR1H Register ....................................................... 189

TMR1L Register ........................................................ 189

Associated registers.................................................. 204

Associated registers.................................................. 204

Timer1

Timer2/4/6

A/D Conversion ......................................................... 374

A/D Conversion (Sleep Mode) .................................. 374

Acknowledge Sequence ........................................... 283

Asynchronous Reception .......................................... 304

Asynchronous Transmission ..................................... 300

Asynchronous Transmission (Back to Back) ............ 301

Auto Wake-up Bit (WUE) During Normal Operation . 316

Auto Wake-up Bit (WUE) During Sleep .................... 316

Automatic Baud Rate Calibration .............................. 314

Baud Rate Generator with Clock Arbitration ............. 276

BRG Reset Due to SDA Arbitration During

Brown-out Reset (BOR) ............................................ 370

Brown-out Reset Situations ........................................ 81

Bus Collision During a Repeated Start Condition

Bus Collision During a Repeated Start Condition

Bus Collision During a Start Condition (SCL = 0) ..... 287

Reading and Writing ......................................... 191

Selecting Source............................................... 191

T1CON.............................................................. 197

T1GCON ........................................................... 198

TXCON ............................................................. 203

Start Condition .................................................. 287

(Case 1) ............................................................ 288

(Case 2) ............................................................ 288

Preliminary

Timing Diagrams and Specifications

Timing Parameter Symbology .......................................... 365

Timing Requirements

TINLVLC Register............................................................. 139

TMR0 Register.................................................................... 33

TMR1H Register ................................................................. 33

TMR1L Register.................................................................. 33

TMR2 Register.................................................................... 33

TMR4 Register.................................................................... 41

TMR6 Register.................................................................... 41

TRIS.................................................................................. 350

TRISA Register........................................................... 34, 126

TRISB ............................................................................... 130

TRISB Register........................................................... 34, 132

TRISC ............................................................................... 135

TRISC Register........................................................... 34, 137

Two-Speed Clock Start-up Mode........................................ 67

TXCON (Timer2/4/6) Register .......................................... 203

TXREG ............................................................................. 299

Bus Collision During a Stop Condition (Case 1) ....... 289

Bus Collision During a Stop Condition (Case 2) ....... 289

Bus Collision During Start Condition (SDA only) ...... 286

Bus Collision for Transmit and Acknowledge ........... 285

CLKOUT and I/O ...................................................... 368

Clock Synchronization .............................................. 273

Clock Timing ............................................................. 366

Comparator Output ................................................... 175

Enhanced Capture/Compare/PWM (ECCP)............. 372

Fail-Safe Clock Monitor (FSCM)................................. 70

First Start Bit Timing ................................................. 277

Full-Bridge PWM Output........................................... 229

Half-Bridge PWM Output .................................. 227, 234

I

I

I

I

I

INT Pin Interrupt ......................................................... 91

Internal Oscillator Switch Timing ................................ 65

PWM Auto-shutdown ................................................ 233

PWM Direction Change ............................................ 230

PWM Direction Change at Near 100% Duty Cycle... 231

PWM Output (Active-High) ....................................... 225

PWM Output (Active-Low) ........................................ 226

Repeat Start Condition ............................................. 278

Reset Start-up Sequence ........................................... 83

Reset, WDT, OST and Power-up Timer ................... 369

Send Break Character Sequence ............................. 317

SPI Master Mode (CKE = 1, SMP = 1) ..................... 377

SPI Mode (Master Mode).......................................... 250

SPI Slave Mode (CKE = 0) ....................................... 378

SPI Slave Mode (CKE = 1) ....................................... 378

Synchronous Reception (Master Mode, SREN) ....... 321

Synchronous Transmission ...................................... 319

Synchronous Transmission (Through TXEN) ........... 319

Timer0 and Timer1 External Clock ........................... 371

Timer1 Incrementing Edge ....................................... 193

Two Speed Start-up.................................................... 68

USART Synchronous Receive (Master/Slave) ......... 376

USART Synchronous Transmission (Master/Slave). 375

Wake-up from Interrupt............................................. 102

PLL Clock ................................................................. 367

I

SPI Mode .................................................................. 379

2

2

2

2

2

2

C Bus Data............................................................. 380

C Bus Start/Stop Bits ............................................. 379

C Master Mode (7 or 10-Bit Transmission) ............ 280

C Master Mode (7-Bit Reception)........................... 282

C Stop Condition Receive or Transmit Mode......... 284

C Bus Data............................................................. 381

Firmware Restart .............................................. 232

2010 Microchip Technology Inc.

Related parts for PIC16F1824-I/P

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC, 8BIT MCU, PIC16F, 32MHZ, SOIC-18

Manufacturer:

Microchip Technology

Datasheet:

Part Number:

Description:

IC, 8BIT MCU, PIC16F, 32MHZ, SSOP-20

Manufacturer:

Microchip Technology

Datasheet:

Part Number:

Description:

IC, 8BIT MCU, PIC16F, 32MHZ, DIP-18

Manufacturer:

Microchip Technology

Datasheet:

Part Number:

Description:

IC, 8BIT MCU, PIC16F, 32MHZ, QFN-28

Manufacturer:

Microchip Technology

Datasheet:

Part Number:

Description:

IC, 8BIT MCU, PIC16F, 32MHZ, QFN-28

Manufacturer:

Microchip Technology

Datasheet:

Part Number:

Description:

IC, 8BIT MCU, PIC16F, 32MHZ, QFN-28

Manufacturer:

Microchip Technology

Datasheet:

Part Number:

Description:

IC, 8BIT MCU, PIC16F, 32MHZ, SSOP-20

Manufacturer:

Microchip Technology

Datasheet:

Part Number:

Description:

IC, 8BIT MCU, PIC16F, 20MHZ, DIP-40

Manufacturer:

Microchip Technology

Datasheet:

Part Number:

Description:

IC, 8BIT MCU, PIC16F, 32MHZ, QFN-28

Manufacturer:

Microchip Technology

Datasheet:

Part Number:

Description:

IC, 8BIT MCU, PIC16F, 20MHZ, MQFP-44

Manufacturer:

Microchip Technology

Datasheet:

Part Number:

Description:

IC, 8BIT MCU, PIC16F, 20MHZ, QFN-20

Manufacturer:

Microchip Technology

Datasheet:

Part Number:

Description:

IC, 8BIT MCU, PIC16F, 32MHZ, QFN-28

Manufacturer:

Microchip Technology

Datasheet:

Part Number:

Description:

MCU 14KB FLASH 768B RAM 64-TQFP

Manufacturer:

Microchip Technology

Datasheet:

Part Number:

Description:

7 KB Flash, 384 Bytes RAM, 32 MHz Int. Osc, 16 I/0, Enhanced Mid Range Core, Low

Manufacturer:

Microchip Technology

Part Number:

Description:

14KB Flash, 512B RAM, 256B EEPROM, LCD, 1.8-5.5V 40 UQFN 5x5x0.5mm TUBE

Manufacturer:

Microchip Technology

Datasheet: