A000047 Arduino, A000047 Datasheet - Page 169

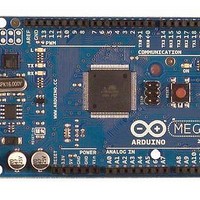

A000047

Manufacturer Part Number

A000047

Description

MCU, MPU & DSP Development Tools Mega2560

Manufacturer

Arduino

Series

-r

Type

MCUr

Specifications of A000047

Processor To Be Evaluated

ATmega2560

Interface Type

USB, I2C, SPI

Dimensions

4 in x 2.1 in

Operating Supply Voltage

5 V

Contents

Board

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

ATmega2560

- Current page: 169 of 444

- Download datasheet (10Mb)

17. Timer/Counter 0, 1, 3, 4, and 5 Prescaler

17.1

17.2

17.3

2549M–AVR–09/10

Internal Clock Source

Prescaler Reset

External Clock Source

Timer/Counter 0, 1, 3, 4, and 5 share the same prescaler module, but the Timer/Counters can

have different prescaler settings. The description below applies to all Timer/Counters. Tn is used

as a general name, n = 0, 1, 3, 4, or 5.

The Timer/Counter can be clocked directly by the system clock (by setting the CSn2:0 = 1). This

provides the fastest operation, with a maximum Timer/Counter clock frequency equal to system

clock frequency (f

clock source. The prescaled clock has a frequency of either f

f

The prescaler is free running, that is, operates independently of the Clock Select logic of the

Timer/Counter, and it is shared by the Timer/Counter Tn. Since the prescaler is not affected by

the Timer/Counter’s clock select, the state of the prescaler will have implications for situations

where a prescaled clock is used. One example of prescaling artifacts occurs when the timer is

enabled and clocked by the prescaler (6 > CSn2:0 > 1). The number of system clock cycles from

when the timer is enabled to the first count occurs can be from 1 to N+1 system clock cycles,

where N equals the prescaler divisor (8, 64, 256, or 1024).

It is possible to use the prescaler reset for synchronizing the Timer/Counter to program execu-

tion. However, care must be taken if the other Timer/Counter that shares the same prescaler

also uses prescaling. A prescaler reset will affect the prescaler period for all Timer/Counters it is

connected to.

An external clock source applied to the Tn pin can be used as Timer/Counter clock (clk

Tn pin is sampled once every system clock cycle by the pin synchronization logic. The synchro-

nized (sampled) signal is then passed through the edge detector.

equivalent block diagram of the Tn synchronization and edge detector logic. The registers are

clocked at the positive edge of the internal system clock (

high period of the internal system clock.

The edge detector generates one clk

= 6) edge it detects.

Figure 17-1. Tn/T0 Pin Sampling

CLK_I/O

Tn

clk

I/O

/1024.

D

LE

CLK_I/O

Q

Synchronization

). Alternatively, one of four taps from the prescaler can be used as a

D

Q

ATmega640/1280/1281/2560/2561

Tn

pulse for each positive (CSn2:0 = 7) or negative (CSn2:0

clk

CLK_I/O

I/O

D

). The latch is transparent in the

Figure 17-1

Q

/8, f

CLK_I/O

Edge Detector

/64, f

shows a functional

CLK_I/O

Tn_sync

(To Clock

Select Logic)

Tn

/256, or

). The

169

Related parts for A000047

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO UNO PROTO PCB REV 3

Manufacturer:

Arduino

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO SHIELD PROTO KIT REV 3

Manufacturer:

Arduino

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO MEGA PROTO KIT REV 3

Manufacturer:

Arduino

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO MEGA PROTO PCB REV 3

Manufacturer:

Arduino

Part Number:

Description:

Development Boards & Kits - AVR ARDUINO STARTER KIT W/ UNO REV3

Manufacturer:

Arduino

Part Number:

Description:

RF Development Tools ARDUINO SHIELD WIRELESS PROTO

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

RF Development Tools ARDUINO SHIELD WIRELESS WITH SD

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

Development Software Getting started w/Arduino

Manufacturer:

Arduino

Part Number:

Description:

Ethernet Modules & Development Tools Ethernet Shield for Arduino

Manufacturer:

Arduino

Part Number:

Description:

MCU, MPU & DSP Development Tools LilyPad Arduino Main Board

Manufacturer:

Arduino

Part Number:

Description:

ARDUINO NANO Board

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

Ethernet Modules & Development Tools ETHERNET SHEILD PoE FOR ARDUINO

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

ATMEGA328 MCU IC W/ Arduino UNO Bootloader

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

Memory Cards MICRO SD CARD 1GB WITH SD ADAPTER

Manufacturer:

Arduino