P80C592FFA/00,512 NXP Semiconductors, P80C592FFA/00,512 Datasheet - Page 101

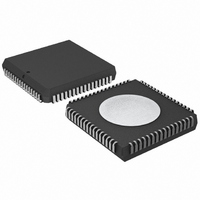

P80C592FFA/00,512

Manufacturer Part Number

P80C592FFA/00,512

Description

IC 80C51 MCU 8BIT ROMLESS 68PLCC

Manufacturer

NXP Semiconductors

Series

80Cr

Datasheet

1.P80C592FFA00512.pdf

(108 pages)

Specifications of P80C592FFA/00,512

Program Memory Type

ROMless

Package / Case

68-PLCC

Core Processor

8051

Core Size

8-Bit

Speed

16MHz

Connectivity

CAN, EBI/EMI, UART/USART

Peripherals

DMA, POR, PWM, WDT

Number Of I /o

48

Ram Size

512 x 8

Voltage - Supply (vcc/vdd)

4.5 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Processor Series

P80C5x

Core

80C51

Data Bus Width

8 bit

Data Ram Size

512 B

Interface Type

CAN/UART

Maximum Clock Frequency

16 MHz

Number Of Programmable I/os

40

Number Of Timers

3

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

PK51, CA51, A51, ULINK2

Minimum Operating Temperature

- 40 C

On-chip Adc

8-ch x 10-bit

Cpu Family

80C

Device Core

80C51

Device Core Size

8b

Frequency (max)

16MHz

Program Memory Size

Not Required

Total Internal Ram Size

512Byte

# I/os (max)

40

Number Of Timers - General Purpose

3

Operating Supply Voltage (typ)

5V

Operating Supply Voltage (max)

5.5V

Operating Supply Voltage (min)

4.5V

Instruction Set Architecture

CISC

Operating Temp Range

-40C to 85C

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Pin Count

68

Package Type

PLCC

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Compliant

Other names

568-1241-5

935086530512

P80C592FFAA

935086530512

P80C592FFAA

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

P80C592FFA/00,512

Manufacturer:

ON

Quantity:

300

Company:

Part Number:

P80C592FFA/00,512

Manufacturer:

NXP Semiconductors

Quantity:

10 000

Philips Semiconductors

1996 Jun 27

LOC

00A0

00A1

00A2

00A5

00A7

00A9

00AB

00AD

00AE

00AF

00B0

00A0

8-bit microcontroller with on-chip CAN

OBJ

54E0

C4

03

2415

83

6007

F5D8

75DB96 133

00

00

LINE SOURCE

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

134

135

136

137

138

139

140

141

142

; determine the destination address in data-memory for the

; message's Data-Field

ANL

SWAP

RR

; this value is used as an index for an array of 8 bytes

; containing the destination-addresses for the 8 different

; messages. Note, that the #RX_ARRAY_OFFSET is due to the

; program counter-relative access to the array.

ADD

MOVC

RX_ARRAY_OFFSET:

; if a message passes the acceptance-filter of the CAN

; Controller, but the CPU doesn't need it, the array

; entry's value may be set to zero indicating this.

; The following jz instruction cares for this.

JZ

; now copy the Data-Field (only) from CAN- to CPU memory

; with the aid of the DMA-logic. Note, that a TX-DMA is

; performed when writing 8AH (DMA + address 10) into CANADR

; and a RX-DMA is performed when writing 94H (DMA + address 20)

; ... 9DH (DMA + address 29) into CANADR. Here address 22 is

; used to copy just the Data-Field.

MOV

MOV

; the DMA-transfer is done in at maximum 2 instruction cycles.

; During the transfer, neither the data-memory (RAM) nor one

; of the SFRs CANADR, CANDAT, CANCON and

; CANSTA may be accessed by the CPU.

; For simplicity, two NOPs are used here.

NOP

NOP

101

A, #ID2_0_MASK

A

A

A, #RX_ARRAY_START

A, @A + PC

CAN_RX_READY

CANSTA, A

CANADR, #CAN_RX_DMA ; starts RX-DMA at address 22

RX_ARRAY_OFFSET

; use ID.2 ... ID.0 only

; A = 4*ID.2 + 2*ID.1 + ID.0

; data-memory address

Product specification

P8xC592