MC908MR32CFUE Freescale Semiconductor, MC908MR32CFUE Datasheet - Page 139

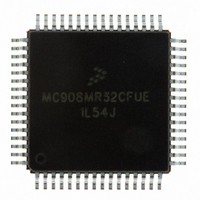

MC908MR32CFUE

Manufacturer Part Number

MC908MR32CFUE

Description

IC MCU 8MHZ 32K FLASH 64-QFP

Manufacturer

Freescale Semiconductor

Series

HC08r

Datasheet

1.MC908MR16CFUE.pdf

(282 pages)

Specifications of MC908MR32CFUE

Core Processor

HC08

Core Size

8-Bit

Speed

8MHz

Connectivity

SCI, SPI

Peripherals

LVD, POR, PWM

Number Of I /o

44

Program Memory Size

32KB (32K x 8)

Program Memory Type

FLASH

Ram Size

768 x 8

Voltage - Supply (vcc/vdd)

4.5 V ~ 5.5 V

Data Converters

A/D 10x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

64-QFP

Processor Series

HC08MR

Core

HC08

Data Bus Width

8 bit

Data Ram Size

768 B

Interface Type

SCI/SPI

Maximum Clock Frequency

8.2 MHz

Number Of Programmable I/os

44

Number Of Timers

6

Operating Supply Voltage

0 V to 5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Development Tools By Supplier

FSICEBASE, M68CBL05CE

Minimum Operating Temperature

- 40 C

On-chip Adc

10-ch x 10-bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC908MR32CFUE

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Part Number:

MC908MR32CFUE

Manufacturer:

NXP/恩智浦

Quantity:

20 000

- Current page: 139 of 282

- Download datasheet (2Mb)

12.6.1.1 Fault Pin Filter

Each fault pin incorporates a filter to assist in determining a genuine fault condition. After a fault pin has

been logic low for one CPU cycle, a rising edge (logic high) will be synchronously sampled once per CPU

cycle for two cycles. If both samples are detected logic high, the corresponding FPIN bit and FFLAG bit

will be set. The FPIN bit will remain set until the corresponding fault pin is logic low and synchronously

sampled once in the following CPU cycle.

12.6.1.2 Automatic Mode

In automatic mode, the PWM(s) are disabled immediately once a filtered fault condition is detected (logic

high). The PWM(s) remain disabled until the filtered fault condition is cleared (logic low) and a new PWM

cycle begins as shown in

PWMs in automatic mode.

The filtered fault pin’s logic state is reflected in the respective FPINx bit. Any write to this bit is overwritten

by the pin state. The FFLAGx event bit is set with each rising edge of the respective fault pin after filtering

has been applied. To clear the FFLAGx bit, the user must write a 1 to the corresponding FTACKx bit.

f the FINTx bit is set, a fault condition resulting in setting the corresponding FFLAG bit will also latch a

CPU interrupt request. The interrupt request latch is not cleared until one of these actions occurs:

Freescale Semiconductor

•

•

•

The FFLAGx bit is cleared by writing a 1 to the corresponding FTACKx bit.

The FINTx bit is cleared. This will not clear the FFLAGx bit.

A reset automatically clears all four interrupt latches.

DISABLE

DISABLE

BANK Y

BANK X

Figure

MC68HC908MR32 • MC68HC908MR16 Data Sheet, Rev. 6.1

Figure 12-27. PWM Disabling Decode Scheme

12-28. Clearing the corresponding FFLAGx event bit will not enable the

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

PWM PIN 5

PWM PIN 1

PWM PIN 4

PWM PIN 2

PWM PIN 3

DISABLE

PWM PIN 6

DISABLE

DISABLE

DISABLE

DISABLE

DISABLE

Fault Protection

139

Related parts for MC908MR32CFUE

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: