MC908MR32CFUE Freescale Semiconductor, MC908MR32CFUE Datasheet - Page 202

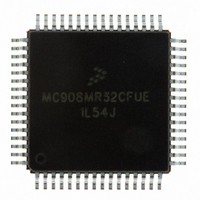

MC908MR32CFUE

Manufacturer Part Number

MC908MR32CFUE

Description

IC MCU 8MHZ 32K FLASH 64-QFP

Manufacturer

Freescale Semiconductor

Series

HC08r

Datasheet

1.MC908MR16CFUE.pdf

(282 pages)

Specifications of MC908MR32CFUE

Core Processor

HC08

Core Size

8-Bit

Speed

8MHz

Connectivity

SCI, SPI

Peripherals

LVD, POR, PWM

Number Of I /o

44

Program Memory Size

32KB (32K x 8)

Program Memory Type

FLASH

Ram Size

768 x 8

Voltage - Supply (vcc/vdd)

4.5 V ~ 5.5 V

Data Converters

A/D 10x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

64-QFP

Processor Series

HC08MR

Core

HC08

Data Bus Width

8 bit

Data Ram Size

768 B

Interface Type

SCI/SPI

Maximum Clock Frequency

8.2 MHz

Number Of Programmable I/os

44

Number Of Timers

6

Operating Supply Voltage

0 V to 5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Development Tools By Supplier

FSICEBASE, M68CBL05CE

Minimum Operating Temperature

- 40 C

On-chip Adc

10-ch x 10-bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC908MR32CFUE

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Part Number:

MC908MR32CFUE

Manufacturer:

NXP/恩智浦

Quantity:

20 000

- Current page: 202 of 282

- Download datasheet (2Mb)

Serial Peripheral Interface Module (SPI)

When CPHA = 1, the first SPSCK cycle begins with an edge on the SPSCK line from its inactive to its

active level. The SPI clock rate (selected by SPR1:SPR0) affects the delay from the write to SPDR and

the start of the SPI transmission. See

derivative of the internal MCU clock. To conserve power, it is enabled only when both the SPE and

SPMSTR bits are set. SPSCK edges occur halfway through the low time of the internal MCU clock. Since

the SPI clock is free-running, it is uncertain where the write to the SPDR occurs relative to the slower

SPSCK. This uncertainty causes the variation in the initiation delay shown in

no longer than a single SPI bit time. That is, the maximum delay is two MCU bus cycles for DIV2, eight

MCU bus cycles for DIV8, 32 MCU bus cycles for DIV32, and 128 MCU bus cycles for DIV128.

202

SPSCK CYCLE

CPHA = 1

CPHA = 0

NUMBER

CLOCK

CLOCK

CLOCK

CLOCK

CLOCK

SPSCK

SPSCK

MOSI

BUS

BUS

BUS

BUS

BUS

TO SPDR

TO SPDR

TO SPDR

TO SPDR

WRITE

WRITE

WRITE

WRITE

TO SPDR

MC68HC908MR32 • MC68HC908MR16 Data Sheet, Rev. 6.1

WRITE

Figure 15-8. Transmission Start Delay (Master)

EARLIEST LATEST

EARLIEST

EARLIEST

EARLIEST

INITIATION DELAY FROM WRITE SPDR TO TRANSFER BEGIN

Figure 15-8

SPSCK = INTERNAL CLOCK ÷ 128;

SPSCK = INTERNAL CLOCK ÷ 32;

INITIATION DELAY

SPSCK = INTERNAL CLOCK ÷ 2;

SPSCK = INTERNAL CLOCK ÷ 8;

128 POSSIBLE START POINTS

32 POSSIBLE START POINTS

2 POSSIBLE START POINTS

8 POSSIBLE START POINTS

MSB

The internal SPI clock in the master is a free-running

1

BIT 6

2

LATEST

LATEST

LATEST

Figure

BIT 5

Freescale Semiconductor

3

15-8. This delay is

Related parts for MC908MR32CFUE

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: