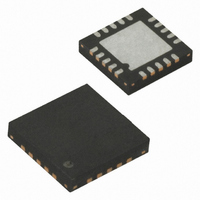

ATTINY4313-MU Atmel, ATTINY4313-MU Datasheet - Page 151

ATTINY4313-MU

Manufacturer Part Number

ATTINY4313-MU

Description

IC MCU AVR 4K FLASH 20QFN

Manufacturer

Atmel

Series

AVR® ATtinyr

Specifications of ATTINY4313-MU

Core Processor

AVR

Core Size

8-Bit

Speed

20MHz

Connectivity

I²C, SPI, UART/USART

Peripherals

Brown-out Detect/Reset, POR, PWM, WDT

Number Of I /o

18

Program Memory Size

4KB (2K x 16)

Program Memory Type

FLASH

Eeprom Size

256 x 8

Ram Size

256 x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 5.5 V

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

20-VQFN Exposed Pad, 20-HVQFN, 20-SQFN, 20-DHVQFN

Processor Series

ATtiny

Core

AVR

Data Bus Width

8 bit

Data Ram Size

256 B

Interface Type

SPI, USART, USI

Maximum Clock Frequency

20 MHz

Number Of Programmable I/os

18

Number Of Timers

2

Operating Supply Voltage

3.3 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Operating Temperature Range

- 40 C to + 85 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Data Converters

-

Lead Free Status / Rohs Status

Details

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ATTINY4313-MU

Manufacturer:

HITTITE

Quantity:

101

- Current page: 151 of 270

- Download datasheet (7Mb)

15.7

8246A–AVR–11/09

AVR USART MSPIM vs. AVR SPI

The USART in MSPIM mode is fully compatible with the AVR SPI regarding:

However, since the USART in MSPIM mode reuses the USART resources, the use of the

USART in MSPIM mode is somewhat different compared to the SPI. In addition to differences of

the control register bits, and that only master operation is supported by the USART in MSPIM

mode, the following features differ between the two modules:

A comparison of the USART in MSPIM mode and the SPI pins is shown in

151.

Table 15-3.

• Master mode timing diagram.

• The UCPOL bit functionality is identical to the SPI CPOL bit.

• The UCPHA bit functionality is identical to the SPI CPHA bit.

• The UDORD bit functionality is identical to the SPI DORD bit.

• The USART in MSPIM mode includes (double) buffering of the transmitter. The SPI has no

• The USART in MSPIM mode receiver includes an additional buffer level.

• The SPI WCOL (Write Collision) bit is not included in USART in MSPIM mode.

• The SPI double speed mode (SPI2X) bit is not included. However, the same effect is

• Interrupt timing is not compatible.

• Pin control differs due to the master only operation of the USART in MSPIM mode.

buffer.

achieved by setting UBRRn accordingly.

USART_MSPIM

(N/A)

XCK

RxD

TxD

Comparison of USART in MSPIM mode and SPI pins.

MOSI

MISO

SCK

SPI

SS

MSPIM

Comment

Master Out only

Master In only

(Functionally identical)

Not supported by USART in

Table 15-3 on page

151

Related parts for ATTINY4313-MU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Atmel Corporation

Datasheet:

Part Number:

Description:

Microcontrollers (MCU) 512B FL 32B SRAM TIMER ATTINY4 12MHz

Manufacturer:

Atmel

Part Number:

Description:

IC MCU AVR 512B FLASH SOT-23-6

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU AVR 512B FLASH SOT-23-6

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet: