ATTINY4313-MU Atmel, ATTINY4313-MU Datasheet - Page 23

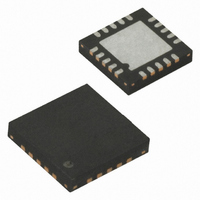

ATTINY4313-MU

Manufacturer Part Number

ATTINY4313-MU

Description

IC MCU AVR 4K FLASH 20QFN

Manufacturer

Atmel

Series

AVR® ATtinyr

Specifications of ATTINY4313-MU

Core Processor

AVR

Core Size

8-Bit

Speed

20MHz

Connectivity

I²C, SPI, UART/USART

Peripherals

Brown-out Detect/Reset, POR, PWM, WDT

Number Of I /o

18

Program Memory Size

4KB (2K x 16)

Program Memory Type

FLASH

Eeprom Size

256 x 8

Ram Size

256 x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 5.5 V

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

20-VQFN Exposed Pad, 20-HVQFN, 20-SQFN, 20-DHVQFN

Processor Series

ATtiny

Core

AVR

Data Bus Width

8 bit

Data Ram Size

256 B

Interface Type

SPI, USART, USI

Maximum Clock Frequency

20 MHz

Number Of Programmable I/os

18

Number Of Timers

2

Operating Supply Voltage

3.3 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Operating Temperature Range

- 40 C to + 85 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Data Converters

-

Lead Free Status / Rohs Status

Details

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ATTINY4313-MU

Manufacturer:

HITTITE

Quantity:

101

- Current page: 23 of 270

- Download datasheet (7Mb)

5.5.4

5.5.5

5.5.6

8246A–AVR–11/09

GPIOR2 – General Purpose I/O Register 2

GPIOR1 – General Purpose I/O Register 1

GPIOR0 – General Purpose I/O Register 0

When EEMPE is set, setting EEPE within four clock cycles will program the EEPROM at the

selected address. If EEMPE is zero, setting EEPE will have no effect. When EEMPE has been

written to one by software, hardware clears the bit to zero after four clock cycles.

• Bit 1 – EEPE: EEPROM Program Enable

The EEPROM Program Enable Signal EEPE is the programming enable signal to the EEPROM.

When EEPE is written, the EEPROM will be programmed according to the EEPMn bits setting.

The EEMPE bit must be written to one before a logical one is written to EEPE, otherwise no

EEPROM write takes place. When the write access time has elapsed, the EEPE bit is cleared

by hardware. When EEPE has been set, the CPU is halted for two cycles before the next

instruction is executed.

• Bit 0 – EERE: EEPROM Read Enable

The EEPROM Read Enable Signal – EERE – is the read strobe to the EEPROM. When the cor-

rect address is set up in the EEAR Register, the EERE bit must be written to one to trigger the

EEPROM read. The EEPROM read access takes one instruction, and the requested data is

available immediately. When the EEPROM is read, the CPU is halted for four cycles before the

next instruction is executed. The user should poll the EEPE bit before starting the read opera-

tion. If a write operation is in progress, it is neither possible to read the EEPROM, nor to change

the EEAR Register.

Bit

0x15 (0x35)

Read/Write

Initial Value

Bit

0x14 (0x34)

Read/Write

Initial Value

Bit

0x13 (0x33)

Read/Write

Initial Value

MSB

MSB

MSB

R/W

R/W

R/W

7

0

7

0

7

0

R/W

R/W

R/W

6

0

6

0

6

0

R/W

R/W

R/W

5

0

5

0

5

0

R/W

R/W

R/W

4

0

4

0

4

0

R/W

R/W

R/W

3

0

3

0

3

0

R/W

R/W

R/W

2

0

2

0

2

0

R/W

R/W

R/W

1

0

1

0

1

0

LSB

R/W

LSB

R/W

LSB

R/W

0

0

0

0

0

0

GPIOR2

GPIOR1

GPIOR0

23

Related parts for ATTINY4313-MU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Atmel Corporation

Datasheet:

Part Number:

Description:

Microcontrollers (MCU) 512B FL 32B SRAM TIMER ATTINY4 12MHz

Manufacturer:

Atmel

Part Number:

Description:

IC MCU AVR 512B FLASH SOT-23-6

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU AVR 512B FLASH SOT-23-6

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet: