ATTINY4313-MU Atmel, ATTINY4313-MU Datasheet - Page 153

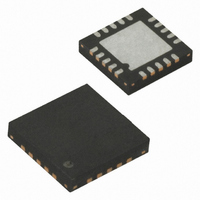

ATTINY4313-MU

Manufacturer Part Number

ATTINY4313-MU

Description

IC MCU AVR 4K FLASH 20QFN

Manufacturer

Atmel

Series

AVR® ATtinyr

Specifications of ATTINY4313-MU

Core Processor

AVR

Core Size

8-Bit

Speed

20MHz

Connectivity

I²C, SPI, UART/USART

Peripherals

Brown-out Detect/Reset, POR, PWM, WDT

Number Of I /o

18

Program Memory Size

4KB (2K x 16)

Program Memory Type

FLASH

Eeprom Size

256 x 8

Ram Size

256 x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 5.5 V

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

20-VQFN Exposed Pad, 20-HVQFN, 20-SQFN, 20-DHVQFN

Processor Series

ATtiny

Core

AVR

Data Bus Width

8 bit

Data Ram Size

256 B

Interface Type

SPI, USART, USI

Maximum Clock Frequency

20 MHz

Number Of Programmable I/os

18

Number Of Timers

2

Operating Supply Voltage

3.3 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Operating Temperature Range

- 40 C to + 85 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Data Converters

-

Lead Free Status / Rohs Status

Details

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ATTINY4313-MU

Manufacturer:

HITTITE

Quantity:

101

- Current page: 153 of 270

- Download datasheet (7Mb)

15.8.4

8246A–AVR–11/09

UCSRC – USART MSPIM Control and Status Register C

• Bit 6 – TXCIE: TX Complete Interrupt Enable

Writing this bit to one enables interrupt on the TXC Flag. A USART Transmit Complete interrupt

will be generated only if the TXCIE bit is written to one, the Global Interrupt Flag in SREG is writ-

ten to one and the TXC bit in UCSRA is set.

• Bit 5 – UDRIE: USART Data Register Empty Interrupt Enable

Writing this bit to one enables interrupt on the UDRE Flag. A Data Register Empty interrupt will

be generated only if the UDRIE bit is written to one, the Global Interrupt Flag in SREG is written

to one and the UDRE bit in UCSRA is set.

• Bit 4 – RXEN: Receiver Enable

Writing this bit to one enables the USART Receiver in MSPIM mode. The Receiver will override

normal port operation for the RxD pin when enabled. Disabling the Receiver will flush the receive

buffer. Only enabling the receiver in MSPI mode (i.e. setting RXEN=1 and TXEN=0) has no

meaning since it is the transmitter that controls the transfer clock and since only master mode is

supported.

• Bit 3 – TXEN: Transmitter Enable

Writing this bit to one enables the USART Transmitter. The Transmitter will override normal port

operation for the TxD pin when enabled. The disabling of the Transmitter (writing TXEN to zero)

will not become effective until ongoing and pending transmissions are completed, i.e., when the

Transmit Shift Register and Transmit Buffer Register do not contain data to be transmitted.

When disabled, the Transmitter will no longer override the TxD port.

• Bit 2:0 – Reserved Bits in MSPI mode

When in MSPI mode, these bits are reserved for future use. For compatibility with future devices,

these bits must be written to zero when UCSRB is written.

• Bit 7:6 – UMSEL1:0: USART Mode Select

These bits select the mode of operation of the USART as shown in

USART Control and Status Register C” on page 139

operation. The MSPIM is enabled when both UMSEL bits are set to one. The UDORD, UCPHA,

and UCPOL can be set in the same write operation where the MSPIM is enabled.

Table 15-4.

Bit

0x03 (0x23)

Read/Write

Initial Value

UMSEL1

UMSEL Bits Settings

UMSEL1

0

0

1

1

R/W

7

0

UMSEL0

R/W

6

0

R

5

0

-

UMSEL0

R

4

0

-

1

0

1

0

R

3

0

-

for full description of the normal USART

UDORD

R/W

2

1

Mode

Asynchronous USART

Synchronous USART

Reserved

Master SPI (MSPIM)

Table

UCPHA

R/W

1

1

15-4. See

UCPOL

R/W

0

0

“UCSRC –

UCSRC

153

Related parts for ATTINY4313-MU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Atmel Corporation

Datasheet:

Part Number:

Description:

Microcontrollers (MCU) 512B FL 32B SRAM TIMER ATTINY4 12MHz

Manufacturer:

Atmel

Part Number:

Description:

IC MCU AVR 512B FLASH SOT-23-6

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU AVR 512B FLASH SOT-23-6

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet: