DEMO9S08JM16 Freescale Semiconductor, DEMO9S08JM16 Datasheet - Page 190

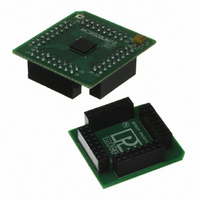

DEMO9S08JM16

Manufacturer Part Number

DEMO9S08JM16

Description

BOARD DEMO FOR JM16 FAMI

Manufacturer

Freescale Semiconductor

Type

MCUr

Datasheets

1.DEMO9S08JM16.pdf

(47 pages)

2.DEMO9S08JM16.pdf

(5 pages)

3.DEMO9S08JM16.pdf

(4 pages)

4.DEMO9S08JM16.pdf

(386 pages)

Specifications of DEMO9S08JM16

Contents

Board with Daughter card, Cable, Documentation, Mini-AB USB Kit

Processor To Be Evaluated

MC9S08JM16

Data Bus Width

8 bit

Interface Type

USB

Silicon Manufacturer

Freescale

Core Architecture

HCS08

Core Sub-architecture

HCS08

Silicon Core Number

MC9S08

Silicon Family Name

Flexis - S08JM

Rohs Compliant

Yes

For Use With/related Products

MC9S08JM16

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- DEMO9S08JM16 PDF datasheet

- DEMO9S08JM16 PDF datasheet #2

- DEMO9S08JM16 PDF datasheet #3

- DEMO9S08JM16 PDF datasheet #4

- Current page: 190 of 386

- Download datasheet (8Mb)

Multi-Purpose Clock Generator (S08MCGV1)

In FLL bypassed external mode, the MCGOUT clock is derived from the external reference clock. The

external reference clock which is enabled can be an external crystal/resonator or it can be another external

clock source.The FLL clock is controlled by the external reference clock, and the FLL clock frequency

locks to 1024 times the reference frequency, as selected by the RDIV bits. The MCGLCLK is derived from

the FLL and the PLL is disabled in a low power state.

12.4.1.5

The PLL engaged external (PEE) mode is entered when all the following conditions occur:

In PLL engaged external mode, the MCGOUT clock is derived from the PLL clock which is controlled by

the external reference clock. The external reference clock which is enabled can be an external

crystal/resonator or it can be another external clock source The PLL clock frequency locks to a

multiplication factor, as selected by the VDIV bits, times the reference frequency, as selected by the RDIV

bits. If BDM is enabled then the MCGLCLK is derived from the DCO (open-loop mode) divided by two.

If BDM is not enabled then the FLL is disabled in a low power state.

190

•

•

•

•

•

•

•

•

•

CLKS bits are written to 10

IREFS bit is written to 0

PLLS bit is written to 0

RDIV bits are written to divide reference clock to be within the range of 31.25 kHz to 39.0625 kHz

LP bit is written to 0

CLKS bits are written to 00

IREFS bit is written to 0

PLLS bit is written to 1

RDIV bits are written to divide reference clock to be within the range of 1 MHz to 2 MHz

PLL Engaged External (PEE)

It is possible to briefly operate in FBE mode with an FLL reference clock

frequency that is greater than the specified maximum frequency. This can be

necessary in applications that operate in PEE mode using an external crystal

with a frequency above 5 MHz. Please see

from FEI to PEE Mode: External Crystal = 8 MHz, Bus Frequency = 8 MHz

for a detailed example.

MC9S08JM16 Series Data Sheet, Rev. 2

NOTE

12.5.2.4, “Example # 4: Moving

Freescale Semiconductor

Related parts for DEMO9S08JM16

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: