MC9S12C128CFUE Freescale Semiconductor, MC9S12C128CFUE Datasheet - Page 172

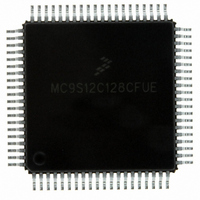

MC9S12C128CFUE

Manufacturer Part Number

MC9S12C128CFUE

Description

IC MCU 128K FLASH 25MHZ 80-QFP

Manufacturer

Freescale Semiconductor

Series

HCS12r

Specifications of MC9S12C128CFUE

Core Processor

HCS12

Core Size

16-Bit

Speed

25MHz

Connectivity

CAN, EBI/EMI, SCI, SPI

Peripherals

POR, PWM, WDT

Number Of I /o

60

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

2.35 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

80-QFP

Cpu Family

HCS12

Device Core Size

16b

Frequency (max)

25MHz

Interface Type

CAN/SCI/SPI

Total Internal Ram Size

4KB

# I/os (max)

60

Number Of Timers - General Purpose

8

Operating Supply Voltage (typ)

2.5/5V

Operating Supply Voltage (max)

2.75/5.5V

Operating Supply Voltage (min)

2.35/2.97V

On-chip Adc

8-chx10-bit

Instruction Set Architecture

CISC

Operating Temp Range

-40C to 85C

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Pin Count

80

Package Type

PQFP

Processor Series

S12C

Core

HCS12

Data Bus Width

16 bit

Data Ram Size

4000 B

Maximum Clock Frequency

25 MHz

Number Of Programmable I/os

61

Number Of Timers

1

Operating Supply Voltage

- 0.3 V to + 6.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

EWHCS12

Development Tools By Supplier

M68EVB912C32EE

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC9S12C128CFUE

Manufacturer:

ST

Quantity:

6 246

Company:

Part Number:

MC9S12C128CFUE

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 172 of 690

- Download datasheet (4Mb)

Chapter 6 Background Debug Module (BDMV4) Block Description

172

CLKSW

UNSEC

Field

PLLSEL

2

1

0

0

1

1

Clock Switch — The CLKSW bit controls which clock the BDM operates with. It is only writable from a hardware

BDM command. A 150 cycle delay at the clock speed that is active during the data portion of the command will

occur before the new clock source is guaranteed to be active. The start of the next BDM command uses the new

clock for timing subsequent BDM communications.

Table 6-3

and reset generator) bits.

Note: The BDM alternate clock source can only be selected when CLKSW = 0 and PLLSEL = 1. The BDM serial

Note: If the acknowledge function is turned on, changing the CLKSW bit will cause the ACK to be at the new rate

Unsecure — This bit is only writable in special single-chip mode from the BDM secure firmware and always gets

reset to zero. It is in a zero state as secure mode is entered so that the secure BDM firmware lookup table is

enabled and put into the memory map along with the standard BDM firmware lookup table.

The secure BDM firmware lookup table verifies that the on-chip EEPROM and FLASH EEPROM are erased. This

being the case, the UNSEC bit is set and the BDM program jumps to the start of the standard BDM firmware

lookup table and the secure BDM firmware lookup table is turned off. If the erase test fails, the UNSEC bit will

not be asserted.

0 System is in a secured mode

1 System is in a unsecured mode

Note: When UNSEC is set, security is off and the user can change the state of the secure bits in the on-chip

interface is now fully synchronized to the alternate clock source, when enabled. This eliminates frequency

restriction on the alternate clock which was required on previous versions. Refer to the device overview

section to determine which clock connects to the alternate clock source input.

for the write command which changes it.

FLASH EEPROM. Note that if the user does not change the state of the bits to “unsecured” mode, the

system will be secured again when it is next taken out of reset.

CLKSW

shows the resulting BDM clock source based on the CLKSW and the PLLSEL (Pll select from the clock

0

1

0

1

Table 6-2. BDMSTS Field Descriptions (continued)

Bus clock

Bus clock

Alternate clock (refer to the device overview chapter to determine the alternate clock

source)

Bus clock dependent on the PLL

MC9S12C-Family / MC9S12GC-Family

Table 6-3. BDM Clock Sources

Rev 01.24

Description

BDMCLK

Freescale Semiconductor

Related parts for MC9S12C128CFUE

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: