MC9S12C128CFUE Freescale Semiconductor, MC9S12C128CFUE Datasheet - Page 346

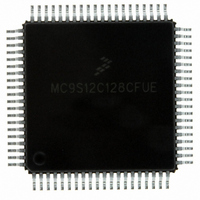

MC9S12C128CFUE

Manufacturer Part Number

MC9S12C128CFUE

Description

IC MCU 128K FLASH 25MHZ 80-QFP

Manufacturer

Freescale Semiconductor

Series

HCS12r

Specifications of MC9S12C128CFUE

Core Processor

HCS12

Core Size

16-Bit

Speed

25MHz

Connectivity

CAN, EBI/EMI, SCI, SPI

Peripherals

POR, PWM, WDT

Number Of I /o

60

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

2.35 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

80-QFP

Cpu Family

HCS12

Device Core Size

16b

Frequency (max)

25MHz

Interface Type

CAN/SCI/SPI

Total Internal Ram Size

4KB

# I/os (max)

60

Number Of Timers - General Purpose

8

Operating Supply Voltage (typ)

2.5/5V

Operating Supply Voltage (max)

2.75/5.5V

Operating Supply Voltage (min)

2.35/2.97V

On-chip Adc

8-chx10-bit

Instruction Set Architecture

CISC

Operating Temp Range

-40C to 85C

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Pin Count

80

Package Type

PQFP

Processor Series

S12C

Core

HCS12

Data Bus Width

16 bit

Data Ram Size

4000 B

Maximum Clock Frequency

25 MHz

Number Of Programmable I/os

61

Number Of Timers

1

Operating Supply Voltage

- 0.3 V to + 6.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

EWHCS12

Development Tools By Supplier

M68EVB912C32EE

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC9S12C128CFUE

Manufacturer:

ST

Quantity:

6 246

Company:

Part Number:

MC9S12C128CFUE

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 346 of 690

- Download datasheet (4Mb)

Chapter 11 Oscillator (OSCV2) Block Description

11.3

The CRG contains the registers and associated bits for controlling and monitoring the OSCV2 module.

11.4

The OSCV2 block has two external pins, EXTAL and XTAL. The oscillator input pin, EXTAL, is intended

to be connected to either a crystal or an external clock source. The selection of Colpitts oscillator or Pierce

oscillator/external clock depends on the XCLKS signal which is sampled during reset. The XTAL pin is

an output signal that provides crystal circuit feedback.

A buffered EXTAL signal, OSCCLK, becomes the internal reference clock. To improve noise immunity,

the oscillator is powered by the V

The Pierce oscillator can be used for higher frequencies compared to the low power Colpitts oscillator.

11.4.1

The Colpitts oscillator is equipped with a feedback system which does not waste current by generating

harmonics. Its configuration is “Colpitts oscillator with translated ground.” The transconductor used is

driven by a current source under the control of a peak detector which will measure the amplitude of the

AC signal appearing on EXTAL node in order to implement an amplitude limitation control (ALC) loop.

The ALC loop is in charge of reducing the quiescent current in the transconductor as a result of an increase

in the oscillation amplitude. The oscillation amplitude can be limited to two values. The normal amplitude

which is intended for non power saving modes and a small amplitude which is intended for low power

operation modes. Please refer to the CRG block description chapter for the control and assignment of the

amplitude value to operation modes.

11.4.2

The clock monitor circuit is based on an internal resistor-capacitor (RC) time delay so that it can operate

without any MCU clocks. If no OSCCLK edges are detected within this RC time delay, the clock monitor

indicates a failure which asserts self clock mode or generates a system reset depending on the state of

SCME bit. If the clock monitor is disabled or the presence of clocks is detected no failure is indicated.The

clock monitor function is enabled/disabled by the CME control bit, described in the CRG block description

chapter.

11.5

OSCV2 contains a clock monitor, which can trigger an interrupt or reset. The control bits and status bits

for the clock monitor are described in the CRG block description chapter.

346

Memory Map and Register Definition

Functional Description

Interrupts

Amplitude Limitation Control (ALC)

Clock Monitor (CM)

DDPLL

MC9S12C-Family / MC9S12GC-Family

and V

SSPLL

Rev 01.24

power supply pins.

Freescale Semiconductor

Related parts for MC9S12C128CFUE

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: